**Swiss Federal Office of Energy SFOE** Energy Research and Cleantech

**Final report**

# **ENMESH**

# Enabling Micro-Concentrator Photovoltaics with Novel Interconnection Methods

Source: Insolight modules on pilot installation ©Insolight 2020

Date: 30th November 2020

Place: Ecublens

Publisher:

Swiss Federal Office of Energy SFOE CH-3003 Bern www.bfe.admin.ch energieforschung@bfe.admin.ch

## Agent:

Insolight SA CH-1024 Ecublens www.insolight.ch

#### Author

Mathieu Ackermann, Insolight SA, mathieu.ackermann@insolight.ch

**SFOE project supervisor:** Stefan Oberholzer, <u>stefan.oberholzer@bfe.admin.ch</u>

SFOE contract number: SI/501620-01

The author of this report bears the entire responsibility for the content and for the conclusions drawn therefrom.

# **Summary**

The Swiss company Insolight is developing a patented PV module that promises a reduction in LCOE for roof-based solar from 0.16€/kWh to 0.011€/kWh. The System uses an array of micro-solar cells with optics and integrated microtracking to produce a low-profile rooftop-compatible solar System with an independently demonstrated efficiency of over 36%, a 100% efficiency gain over cSi. This high efficiency is made possible through the use of advanced multi-junction cells under concentrated light, a technology known as CPV. Specifically, the product represents one of the first commercial examples of micro-CPV (µCPV), wherein the cells are 1mm² in size or less. µCPV increases performance (due to reduced cell operating temperature, higher optical efficiency and lower series resistance losses) and lowers costs.

Insolight innovation has further improved the  $\mu$ CPV concept by embedding sun tracking internally in a 50mm-thick panel, enabling roof-top or BIPV installations and avoiding bulky and expensive trackers. An outstanding technological challenge in  $\mu$ CPV is the need to use massive cell interconnection processes due to the large number of micro-cells involved. The current state of the art is wire bonding, however this inherently serial process is prohibitive for thousands of cells. The Universidad Politecnica de Madrid, in collaboration with Dycotec Materials Ltd, offer an innovative cell interconnection process involving direct printing of ultra-durable nano-particle Coatings Systems to allow the massively parallel connection of solar cells in a cost-effective high volume roll-to-roll or sheet fed printing process, paving the way for the low-cost manufacture of  $\mu$ CPV. They will partner with Insolight in order to develop, test, and validate this interconnection technology, leading to the production of 20cm x 20cm micro-cell boards in a pilot line which will be assembled into a final 10m² demonstrator system.

# Main findings

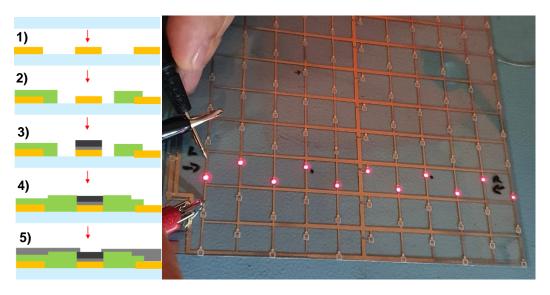

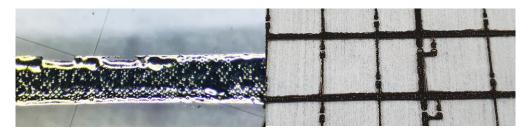

The consortium was able to develop, implement and test a "fully printed" solar cell interconnection process comprising the following steps: 1) a conductive layer is printed on the receiving substrate, 2) a dielectric "dam" is printed in the surroundings of the solar cell pads, 3) solar cells are contacted on the conductive layer using a silver epoxy, 4) syringe filling the surrounding of the cells with a dielectric, and 5) a conductive paste is printed onto the dielectric to connect the front solar cell contact to the underlying circuit.

Figure 1: **Left**: fully printed solar cell interconnection process, **Right**: solar cell light-up test on glass substrate produced using the aforementioned process.

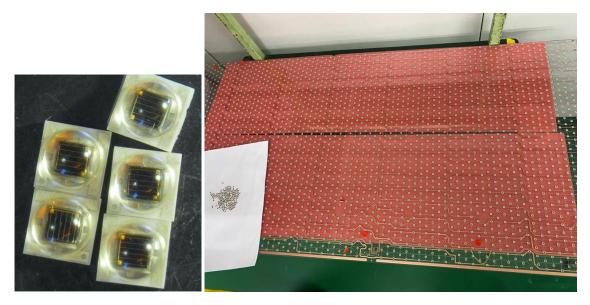

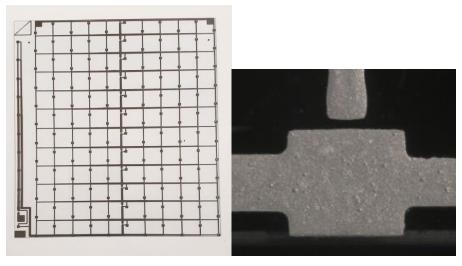

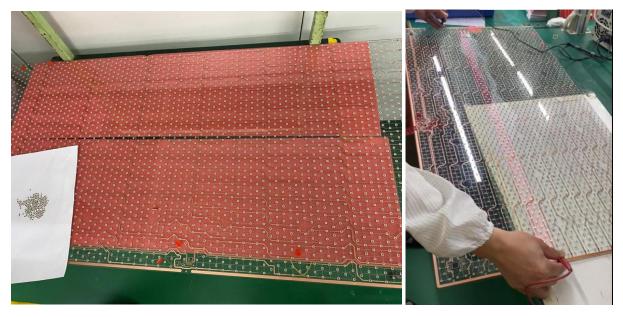

In parallel of the printed process development, another solar cell assembly method has been evaluated: transfering the solar cells from the source wafer to an LED package, then mounting them on a glass substrate by SMT processes (pick & place and reflow soldering). After multiple trials on small glass substrates (ca. 200x200mm), a fully-functional monolithic backplane (ca. 1000x500mm) was successfully designed and manufactured with an external partner.

Figure 2: **Left:** 1x1mm solar cells encapsulated in LED packages. **Right:** monolithic glass substrate with more than 3000 LED-packaged solar cells assembled by SMT processes.

# **Contents**

| Sumn            | mary                                                  | 3  |

|-----------------|-------------------------------------------------------|----|

| Main 1          | findings                                              | 3  |

| Conte           | ents                                                  | 5  |

| Abbre           | eviations                                             | 6  |

| 1               | Introduction                                          | 7  |

| 1.1             | Objectives                                            | 7  |

| 2               | Procedures and methodology                            |    |

| <b>-</b><br>2.1 | Solar cell assembly processes                         |    |

| 2.2             | Solar cell substrates                                 |    |

| 3               | Results and discussion                                |    |

| <b>3</b> .1     | Technical specification                               |    |

| 3.1.1           | Solar cell design                                     |    |

| 3.1.2           | Optical layer                                         |    |

| 3.2             | Development of chemistries for the printing processes |    |

| 3.3             | Test structures                                       |    |

| 3.4             | Single cell boards                                    |    |

| 3.4.1           | Design & manufacturing                                | 14 |

| 3.4.2           | Characterization                                      | 14 |

| 3.4.3           | Overlay issues                                        | 15 |

| 3.5             | Solar cells optimization                              | 16 |

| 3.5.1           | Cell mask optimization and supplier selection         | 16 |

| 3.6             | Full-size cell arrays prototypes                      | 17 |

| 3.6.1           | Arrays based on printed circuit boards (PCBs)         | 17 |

| 3.6.2           | Arrays based on metallized glass substrates           | 18 |

| 3.6.3           | Alternative glass substrates approaches               | 21 |

| 3.7             | SMT process                                           | 22 |

| 3.8             | Full-size backplanes                                  | 23 |

| 3.8.1           | Tiling approach                                       | 23 |

| 3.8.2           | Monolithic approach                                   | 24 |

| 4               | Conclusions                                           | 25 |

| 5               | Outlook                                               | 26 |

| 5.1             | Key achievements                                      | 26 |

| 5.2             | Horizon 2020 (HIPERION)                               | 27 |

| 5.3             | Agrivoltaics                                          | 27 |

| 6               | National and international cooperation                | 28 |

| 6.1 | Consortium     | 28 |

|-----|----------------|----|

| 6.2 | Other Partners | 28 |

| 6.3 | Beyond ENMESH  | 28 |

# **Abbreviations**

| BIPV | Building-Integrated Photovoltaics |

|------|-----------------------------------|

|------|-----------------------------------|

cSi Crystalline Silicon

**LCOE** Levelized Cost of Electricity

LED Light-emitting diode

NCI Nano-printed Cell Interconnections

PCB Printed Circuit Board

SMT Surface-mount technology

µCPV Micro-CPV, Micro-scale Concentrated Photovoltaics

# 1 Introduction

# 1.1 Objectives

The main objective of this project is to enable both the specific technology of Insolight, as well as European MCPV in general, with the development of a **low-cost**, **high-throughput** technology for the **electrical interconnection of large-area solar arrays of micro-solar-cells**, with sizes smaller than 1mm (and as small as 50  $\mu$ m) to be used in  $\mu$ CPV modules, thereby removing a primary hurdle to economic viability of this disruptive and ultra-efficient solar architecture.

Figure 3 the technology developed in the ENMESH project addresses one of the main challenges of the micro-CPV approach: a very large number of solar per meter square have to be assembled and interconnected in a cost-effective manner.

A secondary objective is to pursue **cross-fertilization** between developments of this project and the **LED illumination** sector, allowing chip-on-board modules to move to smaller LED dies and lower interconnection costs. In both LED and CPV, costs can become untenable for very small chips over large areas. In both industries, dies are first packaged onto lead frames or other substrates using pick and place, die attach, and wire bonding. Then these packages must be separated and placed onto a large substrate, in a second pick and place step. This processing chain, an outgrowth of microelectronics heritage, is inherently redundant. The LED world is beginning to move to "chip-on-board" packages, with multiple small dies over a relatively large substrate and no intermediate package. However, the maximum size of these modules is limited in part by the fact that the largest wirebonding equipment cannot accommodate boards larger than a few hundred cm<sup>2</sup>.

The above high-level objectives are translated into the following scientific/technological targets:

- Develop an NCI process and all of the required materials and deposition process to meet the process KPIs defined below.

- Fabricate initial small prototypes which will be subjected to a full set of characterization and qualifications by the UPM experts as well as used for various optimization experiments.

- Perform a pilot manufacturing of 100 full size NCI cell boards.

- Fabricate a 10m<sup>2</sup> Insolight module array for NCI demonstrator which will be installed and grid connected.

- Reliability/qualification tests of materials and components to ensure that NCI meets needs of CPV.

- Develop IP and exploitation plan to pivot to market adoption on project conclusion.

These objectives are evaluated using the following KPIs:

- Efficiency losses compared to conventional processes of no more than 2%

- Meet all relevant qualification standards (including IEC-62108)

- Process capable of 20m²/min throughput in roll-to-roll configuration at 600mm web

- Target cost of 3€/m²

# 2 Procedures and methodology

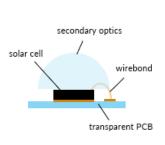

# 2.1 Solar cell assembly processes

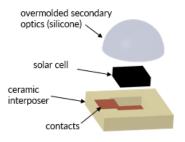

At the start of the project, Insolight modules relied on the chip-on-board approach (1), which consists in transferring the solar cells from the source wafer to the final substrate (PCB), contacting the die to the substrate using a conductive epoxy, then wire-bonding the front contact, and optionally gluing a secondary optical element on top of the cell. This approach is very expensive, as each die must be pick & placed and wire-bonded sequentially. Moreover, wire-bonding machines can only operate on a rather small area (typically 250x250mm), thus limiting the maximum size of the receiving substrate.

During the course of the ENMESH project, several processes have been evaluated:

- An SMT packaging approach (2), leveraging the expertise and economies of scale of the LED industry. While still inherently sequential, this process relies on extremely optimized production equipment with relatively high throughput and yield, providing a significant cost reduction compared to the chip-on-board process (1).

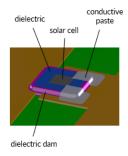

- A printed contact approach (3), where the solar cells are directly mounted on the final substrate and the front contact is connected by a printed conductive paste. This approach has the potential of very high throughput and extremely low assembly costs per meter square, thanks to its parallel processing.

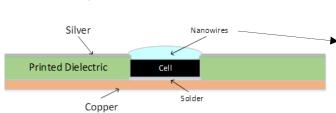

- A printed contact approach combined with a nanowire coating (4). This approach is similar to 3), except that the solar cell front metallization is replaced by a nanowire coating, with the potential benefit of increased efficiency (active area shading is reduced).

## 1) Chip-on-board

- Sequential processExpensive

- Limited area

- Secondary optics possible

## 2) SMT packaging

- Sequential process

- Leveraging LED industry expertise and volumes

- Secondary optics possible

## 3) Printed contacts

- Massively parallel

- High throughput

- Low cost per m<sup>2</sup>

#### 4) Printed nanowire coating

Massively parallel

High throughput

Low cost per m<sup>2</sup>

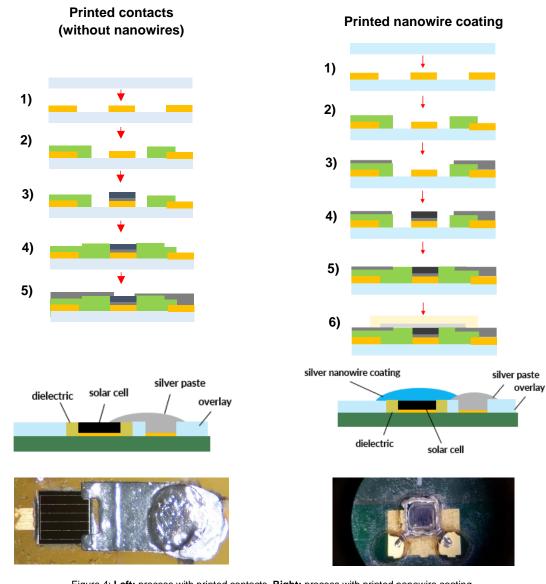

Figure 4 illustrates the two fully printed processes:

- **Printed contacts** (left): 1) a conductive layer is printed on the receiving substrate, 2) a dielectric "dam" is printed in the surroundings of the solar cell pads, 3) solar cells are contacted on the conductive layer using a silver epoxy, 4) the surrounding of the cells are filled with a dielectric, and 5) a conductive paste is printed onto the dielectric to connect the front solar cell contact to the underlying circuit.

- **Printed nanowire coating** (right): 1) a conductive layer is printed on the receiving substrate, 2) a dielectric "dam" is printed in the surroundings of the solar cell pads, 3) a conductive silver paste is printed on top of the dielectric, 4) solar cells are contacted on the conductive layer using a silver epoxy, 5) the surrounding of the cells are filled with a dielectric, and 6) the nanowire coating is printed on top of the solar cell with an overcoat for protection.

Figure 4: Left: process with printed contacts. Right: process with printed nanowire coating.

#### 2.2 Solar cell substrates

During the first year of the project, all the initial process development were performed on conventional Printed Circuit Boards (PCBs) or Insulated Metal Substrates (IMS). Over the course of the project, Insolight operated a strategic shift in market focus from rooftop applications to translucent photovoltaic modules for agrivoltaics. One key requirement for this new market is to have a transparent solar cell substrate, to be able to transmit light through the module. Therefore, the consortium decided to make changes to the initial process flow and develop a fully printed approach, replacing printed circuit boards (PCBs) by a printed glass substrate.

Several approaches were investigated to define a conductive interconnection layer on glass:

- screen-printing of a conductive silver paste (process developed by partner Dycotec)

- screen-printing and annealing of a conductive ceramic (sub-contractor)

- lamination and etching of Copper sheet on glass (sub-contractor)

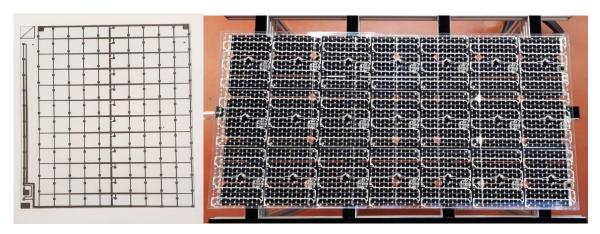

Another important aspect is the size of the solar cell substrates. The initial approach consisted in manufacturing small substrates with dimensions of ca. 20x20cm and providing interconnections for ca. 150 solar cells. The substrates where then assembled together mechanically, or laminated onto a larger substrate to form a complete backplane. However, this tiling approach has two main drawbacks: it requires an extra assembly step – which increases the overall cost – and the relative placement of two such "tiles" must be very accurate, in order to match the positioning of the lenses on the optical layer. Therefore, additional efforts were targeted towards the manufacturing of a "monolithic" glass substrate with the same size as the final solar module (ca. 0.6m²).

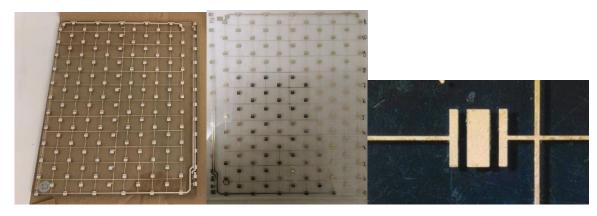

Figure 5: **Left:** small «tiled» glass substrate with interconnections for ca. 150 solar cells. **Right:** complete solar module backplane composed of 21 small glass substrates laminated side-by-side on 3 rows and 7 columns.

# 3 Results and discussion

# 3.1 Technical specification

The first step of the project consisted in establishing a detailed technical specification as a basis for the development of the novel solar cell interconnection processes. Below is a summary of the content of this document.

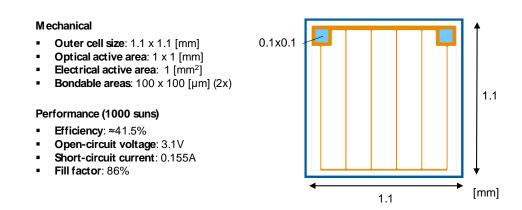

#### 3.1.1 Solar cell design

Information on the existing solar cell design (dimensions, spectral response, etc.) and the current assembly concept (wire bond + die attach) as a basis for further process developments.

Figure 6: Current solar cell design.

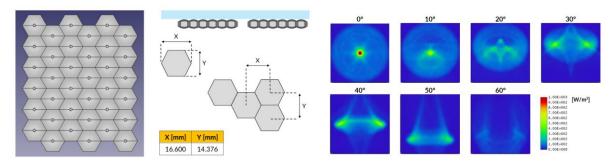

## 3.1.2 Optical layer

Simulations of the focal spot for various sunlight incidence angles and different spectral bands, in order to help defining the required solar cell metallization layout.

Figure 7: Optical layer dimensions and simulations of the focal spot irradiance distribution at various sunlight incidence angles.

# 3.2 Development of chemistries for the printing processes

4 chemistries have been developed by partner Dycotec for the different components of the ENMESH technology:

- a dielectric coating to passivate the solar cell edges

- a silver paste to contact the top of the solar cells with the substrate

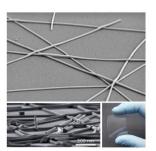

- a conductive transparent layer with silver nanowires to contact the active area of the solar cell

- an overcoat layer to protect the SNW layer

All the selected materials have to meet the general specification below, related to PV qualification tests (IEC norm).

| Test Name                                                              | Test Description                                                                                                                                            | Criteria                                      | Remarks                                                                                                                        |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| High Temperature<br>Storage (IEC<br>60749-6<br>customized to<br>140°C) | 1,000 hours at 140°C, number of samples = 32                                                                                                                | No major<br>visual<br>defects<br>Power<br><5% | Measure resistance change for conductive inks                                                                                  |

| Thermal Cycling<br>(IEC 62108 Annex<br>A)                              | T = -40°C to 110°C, dwell > 5<br>min within ±3°C of extremes.<br>Nominal 2,000 cycles, exact<br>number can vary based on<br>temp rate of change during test | No major<br>visual<br>defects<br>Power<br><5% | Measure resistance change for conductive inks                                                                                  |

| Damp Heat (IEC 62108)                                                  | 1,000 hours at 85°C, 85% RH                                                                                                                                 | No major<br>visual<br>defects<br>Power<br><5% | Measure resistance change for conductive inks                                                                                  |

| Illumination                                                           | 500 h illumination (at nominal concentration conditions) and at open circuit voltage with a solar cell temperature of 90°C                                  | No major<br>visual<br>defects<br>Power<br><5% | Require specialist testing – require tests to be undertaken at IES. Test SNW with overcoat and silver bus-bar systems combined |

Tableau 1: General ENMESH materials specification and corresponding test description.

After extensive testing, Dycotec has performed a down-selection of the chemistries for each layer.

| Layer                  | Chemistry                                                                                                                                                                 | Production Process                                        |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Dielectric Layer       | Epoxy (down-selected option) Polyurethane (Q3 STOP development, unstable) Polysiloxane (Q1 STOP – no further development) Polysilazane (Q2 STOP – no further development) | Syringe dispense (most likely)<br>Stencil print (back-up) |

| Silver Conductive      | Organic Free Silver (Q3 – STOP development,<br>could not obtain additives)<br>Thermoset Silver (back up)<br>High Resolution thermoplastic (preferred)                     | Screen print                                              |

| Transparent Conductive | Silver Nanowire<br>Low viscosity spray (preferred)<br>Screen print (back-up)                                                                                              | Spray (preferred)<br>Screen/stencil print                 |

| Overcoat               | Epoxy (abandoned Q3 – light stability, yellowing) Polyurethane (down-selected)                                                                                            | Syringe/Spray (preferred)<br>Screen print                 |

Figure 8: Down-selection of the chemistries for each layer of the NCI process.

#### Dielectric coating

The materials evaluated included epoxy, polysiloxane, polysiloxane and polyurethane. Epoxy has been selected after extensive UV durability testing. Syringe dispensing is foreseen.

#### Silver paste development

Three different chemistries have been considered here, with either a thermoset silver paste, a high resolution thermoplastic silver paste or an organic binder free system. These various approaches have been evaluated against criteria such as adhesion on substrate, sheet resistivity and viscosity. The thermoplastic is the preferred solution, with a screen printing deposition process.

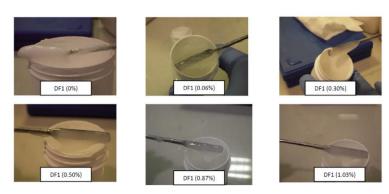

#### **Transparent SNW coating**

Many silver nanowire and solvent formulations are being evaluated on criteria such as sheet resistance, optical transmission and sheet resistance. A spraying system has been purchased by Dycotec for dispensing low-viscosity formulations (preferred approach) and is currently under testing.

#### Overcoat

The overcoat chemistry has to be optically clear on a broad spectrum, to withstand about 100°C, be stable under UV light and protect the assembly from moisture ingress and corrosion. Epoxy, polyurethanes and silicones have been considered for testing. Polyurethane is currently the preferred solution, but silicone will also be evaluated.

Figure 9: silver nano-wires formulations.

## 3.3 Test structures

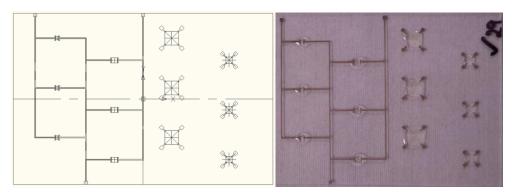

Two types of test structures have designed and printed on glass substrates:

- van der Pauw structures to measure the resistance and transmittance of the nanowire coating

- structures to measure the interconnection of the nanowires with the solar cell front contacts

Figure 10: Left: sketch of the test structures for the NCI process. Right: actual test structure printed on glass substrate.

# 3.4 Single cell boards

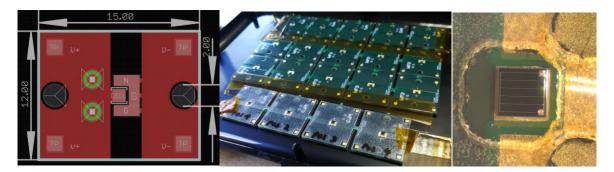

#### 3.4.1 Design & manufacturing

A small printed circuit board (PCB) with contact pads for a single solar cell has been designed. The purpose of these boards was to perform trials of dielectric deposition and solar cell contacting.

The mini-boards have been designed, manufactured and populated with 1x1mm solar cells. The overlay in this case was a perforated film of PET applied semi-manually by UPM. Then Dycotec processed some of the boards with the silver nanowire approach, and some with the nanowire-less approach.

Figure 11: Left: layout of a single solar cell board. Middle: single cell boards populated with solar cells. Right: close-up on solar cell surrounded by PET overlay.

#### 3.4.2 Characterization

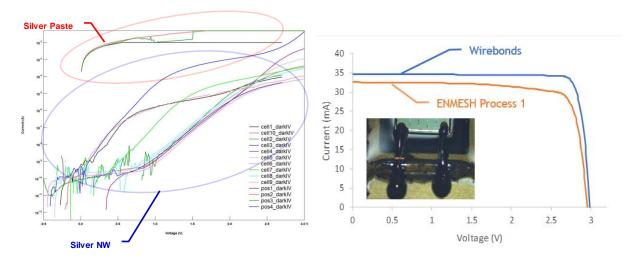

Dycotec processed the mini-boards and sent them to UPM for characterization (IV curve tracing). Both approaches (with and without nanowires) have been tested in parallel. These measurements raised two main issues:

For the nanoprinted cell coating approach, the anti-reflective coating on the surface of the cell prevents good contact between the active area of the cell and the nanowires. Therefore,

- the contact resistance is high and the performance is poor. This confirms that a custom solar cell without anti-reflective coating is required to validate this approach.

- For the printed contact approach (without nanowires), the performance was better, however some boards were partially or totally shunted, most probably because the edge of the solar cells was not completely covered/protected by dielectric material. Applying the dielectric uniformly all around the solar cell without overlap on the active area requires an improved dispensing process.

Figure 12: Left: dark IV curves for boards processed with both silver nanowires and nanowire-less approaches. Right: a comparison of light IV curves on a board with conventional interconnection (wirebonds) and the nanowire-less process.

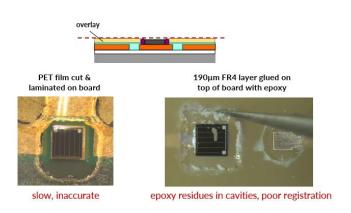

#### 3.4.3 Overlay issues

One of the biggest challenges with any screen printing process is that it requires a "leveling" of the board surface. In other words, the surface should be flat, with no protrusion greater than 10-20µm. This is not trivial, since a typical solar cell is approximately 200µm thick. An overlay is therefore required to increase the thickness of the board to the level of the solar cell front surface. Several types of overlays have been considered and tested, such as PET films or extra FR4

layers with cavities for the cells. However, the overlay application process was typically slow and not accurate.

Finally, the consortium decided to order cells from another vendor with thickness of approximately 30µm. This approach enabled the use of a much thinner overlay and therefore simpler deposition processes such as flood coating.

# 3.5 Solar cells optimization

While initial tests were performed with solar cells already available at the beginning of the project, a dedicated cell design was developed during the course of the project to accommodate the specific requirements of the printed solar cell interconnection processes.

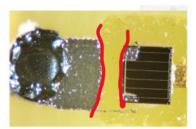

## 3.5.1 Cell mask optimization and supplier selection

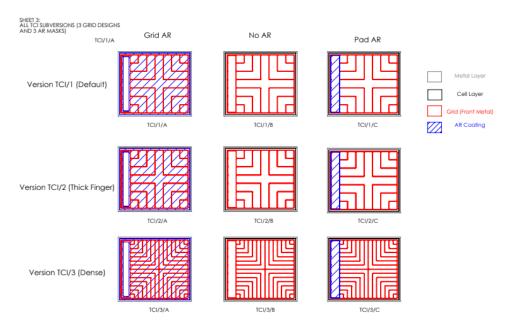

The optimal metallization depends on the technical approach chosen for the NCI process: the silver paste printing requires at least one front contact pad and several grid lines for current collection, while the nanowire coating does not require any grid lines at all. Therefore, multiple metallization designs have been included on the same solar cell mask set (several designs on the same wafer).

Figure 13: solar cell grid designs prepared by UPM for the project

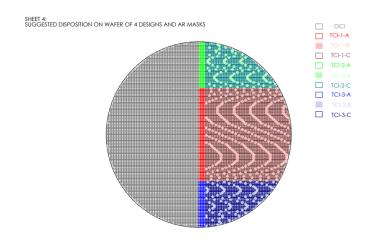

The different solar cell designs were arranged on different quarters of the same wafer.

Figure 14: disposition of solar cell grid designs on wafer mask

After multiple discussions with Azur Space (DE), it became clear that they were not the right supplier for this project:

- Their offer for the solar cell customization package was much more expensive than anticipated in the project budget.

- They were not willing to work flexibly on multi-design approaches required for maximizing the learnings about ENMESH technology (such as cells without AR coating).

- In order to facilitate the printed interconnection process, the consortium decided to use thinner (30μm) solar cells that Azur Space was not able to provide.

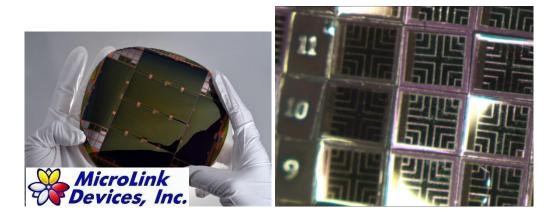

For all the above reasons, the consortium selected MicroLink, a US-based company, capable of delivering thinner solar cells and more open to process customizations.

Figure 15: **Left:** thin flexible high-efficiency III-V solar cells from MicroLink Devices, Inc. **Right:** close-up picture of cells manufactured by MicroLink for the ENMESH project.

# 3.6 Full-size cell arrays prototypes

#### 3.6.1 Arrays based on printed circuit boards (PCBs)

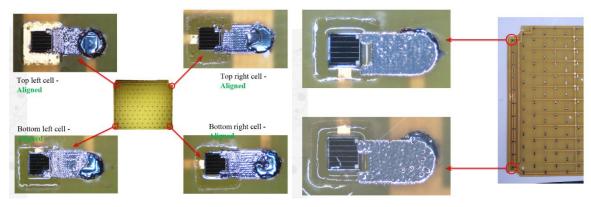

Large printed circuit boards have been designed, manufactured and populated with 143 solar cells of 1x1mm. At this point, the new cells from MicroLink were not yet available and conventional 200um thick solar cells from Azur Space were used instead. The overlay in this case was a thin FR4 layer (ca. 190µm) laminated by the board manufacturer. Dycotec designed a screen to print silver paste for all the solar cell interconnections in one pass.

Figure 16: close-ups of several solar cells on the large 143-cell board, interconnected with the printed contact approach.

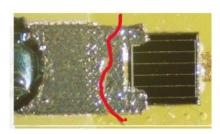

In general, a good registration was achieved on most of the solar cells, except the far-left row of the board. However, several issues were detected, such as cracks and adhesion failures. These issues are attributed to the inhomogeneous dielectric filling of the cavities surrounding the cells.

Figure 17: close-ups on cracks and other silver paste printing issues

This approach was not evaluated further as the thinner solar cells became available and the focus of the project shifted from PCBs to glass substrates.

#### 3.6.2 Arrays based on metallized glass substrates

As described in previous sections, the new focus of Insolight towards translucent modules for agrivoltaics applications induced a change of substrate from conventional printed circuit boards (PCBs) to metallized glass sheets.

For this new approach, Dycotec developed a process to print a silver-based conductive paste onto a glass substrate. As illustrated on Figure 18, the full printing process requires 3 masks:

- 1. Mask for the solar cell interconnection circuit on glass (conductive silver paste).

- 2. Mask for the dielectric "dam" surrounding the solar cells.

- 3. Mask for the front solar cell contact interconnection.

Figure 18: Masks designed for the various steps of the printed contact process on glass.

Several issues were encountered during the development of the silver paste printing process on glass, such as uneven surface, or leaking/flooding causing shorts between adjacent pads.

Figure 19: some of the issues encountered during the development of the silver paste printing process on glass substrates.

After multiple trials the print quality was considered sufficient.

Figure 20: Glass substrate with printed metal layer (silver paste) manufactured by Dycotec (left), and detail of a solar cell pad demonstrating printing accuracy (right).

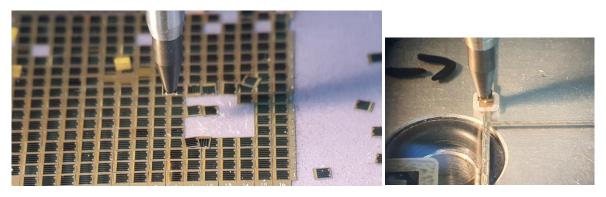

Once a sufficient print quality was achieved on the silver paste printing, the glass substrates were populated by pick & place with thin solar cells from MicroLink. The die attach was performed with a silver-filled epoxy paste.

Figure 21: Pick & place and die attach of solar cells on metallized glass substrate.

The dielectric «dam» around the solar cells was applied by a syringe and UV cured. This is the only non-parallel step of the solar cell interconnection process.

Figure 22: Left: UV curable dielectric filled by syringe around the solar cell. Right: after UV curing.

Finally, the front contact of the solar cell was connected to the underlying circuit by printing a silver paste on top of the dielectric dam.

The complete process was applied on several glass substrates and successfull cell interconnection could be demonstrated by simple light-up tests. Further board characterization such as dark IV and light IV will be performed by UPM in December 2020 to assess the quality of the interconnection and compare the results with conventional processes.

Figure 23: Left: fully interconnected solar cell on metallized glass substrate. Right: light-up test performed on entire row of solar cells.

#### 3.6.3 Alternative glass substrates approaches

In parallel to the silver paste printing approach developed by Dycotec, several other technologies to print a conductive circuit on glass were evaluated with sub-contractors:

- Conductive ceramic paste cured at high temperature (during glass tempering process).

- Copper layer deposited by electroplating.

- Copper sheet laminated on glass and etched to form the final circuit.

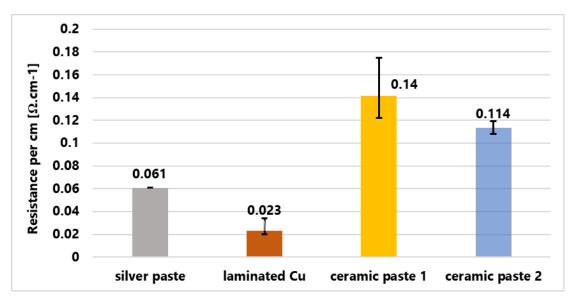

Figure 24: Glass substrates with conductive ceramic paste (left), electroplated Copper (middle) and laminated Copper layer (right).

All technologies were benchmarked on electrical conductivity and reliability, through typical aging tests such as damp heat (85°C, 85%RH) and thermal cycling (from -40 to +85°C). The boards with laminated Copper demonstrated the best conductivity, but also very good stability in both humid and hot conditions.

All types of boards were compatible with conventional reflow soldering processes, although the laminated Copper demonstrated the best solderability.

Figure 25: Resistivity benchmark for various types of print-on-glass technologies.

# 3.7 SMT process

Due to the technical challenges and delays encountered while developing the NCI process, it was critical for Insolight to investigate alternative approaches with the potential to reduce costs for the solar cells interconnection and assembly.

One such approach is the packaging of solar cells using substrates similar to the ones used in the LED industry. Indeed, the requirements in terms of power dissipation, positioning accuracy and light transmission are similar for uCPV and multi-LED panels. Moreover, the LED industry follows a similar trend of reducing the size of the diodes and increasing the density of components per unit area, with strong pressure on cost and extremely high production volumes.

Therefore, several types of packages were evaluated in terms of performance (electrical conductivity, light transmission, power dissipation) and cost, with various types of substrates (plastic, ceramic, etc.) and silicone overmolding shapes.

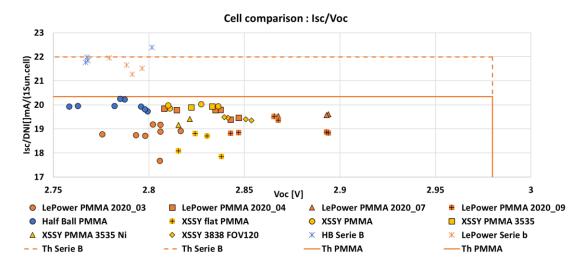

Finally, we selected a package with an alumina substrate and half-ball optics with a field-of-view of approximately 120°, with a potential for costs in volumes below 5ct per unit.

Figure 26: **Left:** various LED packages tested during the project. **Right:** selected packaging solution with alumina substrate and half-ball silicone-based optics.

The packages were benchmarked for instance on the short-circuit current and open-circuit voltage at similar illumination conditions.

Figure 27: Short-circuit current versus open-circuit voltage for various packages.

# 3.8 Full-size backplanes

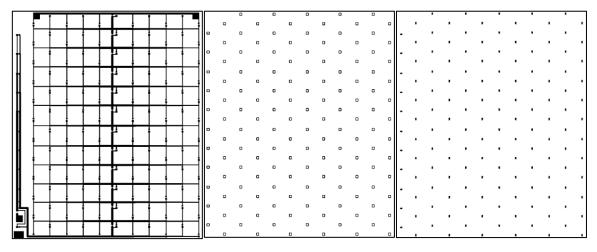

#### 3.8.1 Tiling approach

In this approach, solar cells are first assembled on glass "tiles" which are subsequently laminated together on a larger glass substrate to form a complete backplane. This process was successfully implemented to produce several solar modules.

Figure 28: Fully assembled backplane with 21 glass boards laminated side-by-side on 3 rows and 7 columns.

While the method works and meets the technical requirements of the application, it has several drawbacks:

- The tiles must be very accurately positioned with reference to each other, in order to ensure a

constant "pitch" between solar cells of different boards and to ensure proper alignment with

the optical layer. This is typically achieved with a dedicated mold that holds the glass

substrates together during lamination.

- The lamination process itself takes ca. 20min per backplane, which has a significant cost and limits the overall module assembly throughput.

- The total thickness of glass on the final backplane is typically >3mm, which increases the weight of the solar module.

- The gaps between the glass tiles could lead to water infiltration issues in humid environments.

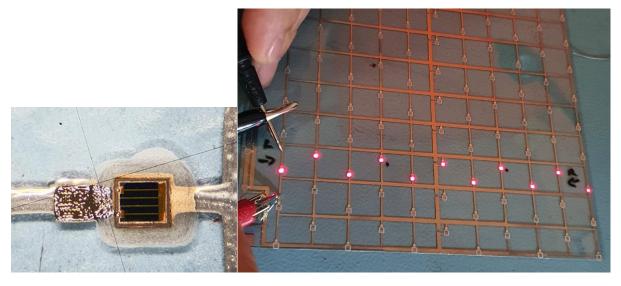

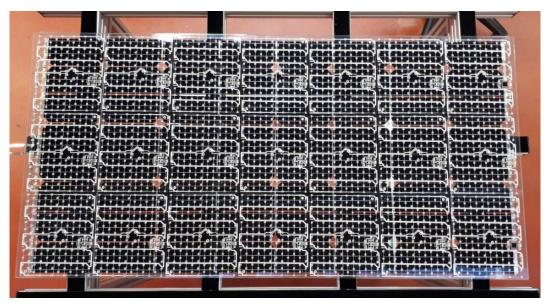

#### 3.8.2 Monolithic approach

As an alternative to the tiling approach, we designed a monolithic backplane, made of a single sheet of tempered glass, onto which a conductive interconnection for all 3000+ solar cells of the modules were printed. We faced several technical challenges:

- The print must be very accurate, with less than ±200µm of absolute error on a total length of more than 1 meter.

- The print must withstand environmental qualification tests such as thermal cycling and humidity soaking.

- The pick & place and reflow soldering equipment at the supplier must capable of handling glass substrates of this size.

Figure 29: Monolithic backplane on glass and close-up on delamination issue.

After multiple trials with different suppliers, in November 2020 we were finally able to get a fully functional monolithic backplane with more than 3000 solar cells correctly interconnected. This is considered a major achievement towards reducing the assembly cost and alignment accuracy of our translucent modules.

Figure 30: **Left:** monolithic glass substrate with more than 3000 LED-packaged solar cells assembled by SMT processes. **Right:** Light-up test performed on the monolithic backplane.

# 4 Conclusions

Although the project suffered from multiple delays, initially due to administrative issues in the grant process of the national funding agencies of our partners UPM in Spain and Dycotec in UK, and towards the end related to the Covid crisis, the consortium was still able to achieve some key results:

- Developing the required chemistries to interconnect solar cells using almost exclusively parallel processes (printed contacts).

- Assembling complete solar cell boards interconnected using the developed processes.

- Designing and manufacturing metallized glass sheets as solar cell substrates.

The following solar cell interconnection methods were evaluated:

- Printed contacts (without nanowires): the process could be demonstrated at board level (several rows of solar cells were successfully interconnected). It is almost fully parallel, except for the filling of the dielectric "dam" surrounding the solar cells, which is currently done by syringe. The actual performance of the interconnection will be evaluated in the last couple of months of the project by partner UPM. The main challenge remaining is to stabilize the process in order to guarantee a precise passivation of the solar cell edges by the dielectric (to avoid shunts) and an accurate interconnection of the front solar cell contact (ensuring proper connection without shading of the active area) when producing large volumes of boards at high speed.

- Printed nanowire cell interconnection: this process could only be demonstrated on single

cells and with poor results due to the anti-reflective coating on the solar cell surface. While

results on the customized solar cells were expected in 2020, due to the coronavirus crisis the

consortium focused all efforts on the printed contact approach. The potential efficiency gain of

removing the front solar cell metallization could not be demonstrated due to lack of time.

- **SMT process:** several LED packaging solutions were evaluated and one option selected based on techno-economical criteria. Thousands of solar cells were packaged and assembled on glass substrates by pick & place and reflow soldering. Although it is not fully clear if this approach can reach the cost targets required for mass production, this is the process used by Insolight to build its pre-series of modules.

The partners have agreed to extend their collaboration beyond the end of ENMESH in order to finalize the tests that are already in progress and get more definitive results on the feasibility and performance of the fully printed solar cell interconnections processes developed during the project. Insolight remains very interested by the potential of these processes to further decrease the assembly costs of its uCPV modules.

# 5 Outlook

# 5.1 Key achievements

On a more global scope, a lot of progress has been made by Insolight over the years 2018-2020 towards the development of highly-efficient and translucent solar modules, focusing not only on raw performance but also on reliability and compatibility with industrial processes:

- A total of 3 pilot installations are running at EPFL (Lausanne, Switzerland), Fraunhofer ISE (Freiburg, Germany) and UPM (Madrid, Spain). The oldest modules have been operating for almost 3 years, enduring tough winter conditions, as well as hot summer months and strong rainstorms.

- In November 2018, an Insolight module has been rated by UPM at 29% efficiency in CSTC conditions, a potential world record for a large-scale fixed-tilt module.

- Pre-qualification tests (temperature cycling, damp heat, etc.) at component level (optics, adhesives, etc.) have started in early 2019 in collaboration with CSEM and SUPSI.

- More than 30 pre-series modules have been produced in 2020 with a contract manufacturer.

Figure 31: Insolight modules installed at UPM in Madrid (top-left), Conthey (top-right) and at EPFL in Lausanne (bottom).

# 5.2 Horizon 2020 (HIPERION)

Insolight has assembled a consortium of 16 European partners (including research centers, industrial companies and end users) and submitted a successful proposal for an Horizon 2020 call focusing on developing a pilot manufacturing line for its high efficiency modules. The project kicked-off in September 2019 and will last 4 years, with a total funding of more than 10k€.

An entire work package in HIPERION is dedicated to investigating various cell technologies and assembly processes to cost-effectively assemble thousand of tiny solar cells per module, building on the findings of the ENMESH project.

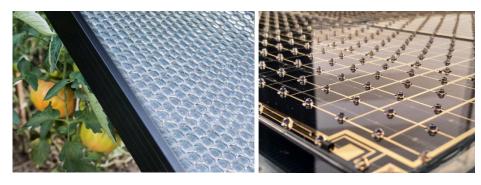

# 5.3 Agrivoltaics

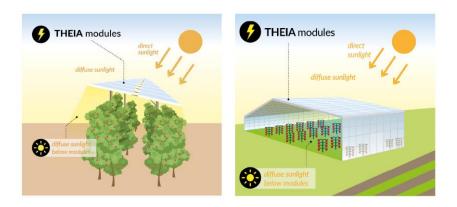

Thanks to their translucency and integrated sun tracking mechanisms, Insolight modules are ideally suited for agrivoltaics installations, where solar modules are deployed above existing cultures or on the roof of greenhouses. The monolithic glass substrate developed during the ENMESH project is a key component of this translucent module architecture, enabling the harvesting of direct sunlight of high efficiency solar cells, while transmitting most of diffuse sunlight to the crops below.

Figure 32: Insolight's THEIA modules for agrivoltaics.

# 6 National and international cooperation

#### 6.1 Consortium

- Universidad Politecnica de Madrid has 30 years of experience in the development and characterization of CPV systems and an established place at the cutting edge of CPV research, having coordinated many large EU-funded CPV-specific projects. In the μCPV space, the group has worked under commercial contract with two companies and one research institute developing μCPV, including Semprius. UPM researchers invented the NCI process and will use their multi-disciplinary expertise in the wide range of CPV requirements to develop a detailed specification of the process. Their deep knowledge of CPV characterization will serve to characterize and validate the arrays of cells interconnected with NCI.

- Dycotec Materials Ltd develops and manufactures the advanced materials solutions DML are already supplying conductive inks and insulator layers for thin film solar manufacturers of CIGS and CdTe, and developing tailored formulations for perovskite manufacturers and involved in an Innovate funded (UK Govt) project, INTREPID, which aims to provide novel efficiency enhancing coatings to the PV industry. DML will use their state-of-the-art laboratory and production facilities for the research, formulation, and characterization of conductive inks, barrier layers and insulating layers, which are vital for the UPM concept. Their deep experience to derive material sets is required to realize the NCI process, particularly the four discrete ink formulations.

- Insolight SA is a Swiss startup backed by several private and public funds in Switzerland and Europe, including the European Space Agency Business Incubation Centre (ESA BIC). Insolight has developed a patented high efficiency PV module with integrated micro-tracking, allowing μCPV to be integrated into residential and commercial settings. As one of the first European developers of μCPV, their product is uniquely position to benefit from the technology being developed by UPM and Dycotec, and Insolight views ENMESH as critical to enable mass adoption of their μCPV products. Within the project, Insolight will primarily act as a final customer, defining requirements for the NCI technology and providing the μCPV systems into which it can inserted, and validating performance. Their participation is crucial to allow us to demonstrate a TRL6 at the close of the project.

## 6.2 Other Partners

- Dow Corning (Belgium): manufacturer of the high transmission silicone rubber used for our optical layer, they are also supporting us in developing an optimal silicone-on-glass assembly process.

- MicroLink (USA): manufacturer of extremely thin (ca. 30um thick) high-efficiency multijunction solar cells, based on lift-off process. Supplier selected to manufacture the cells with custom metallization required for the ENMESH project.

- **Topsil** (Poland): injection molding expert, manufactures high-quality optical molds for the injection of our lens arrays in silicone rubber.

# 6.3 Beyond ENMESH

As described in the previous section, the ENMESH project was an entry door to larger international collaborations for Insolight. For instance, UPM introduced us to Mondragon Assembly, a major PV equipment manufacturer in Spain, which was the starting point of the consortium we assembled for the HIPERION project.