Schweizerische Eidgenossenschaft

Confédération suisse

Confederazione Svizzera

Confederaziun svizra

Department of the Environment, Transport, Energy and

Communication DETEC

Swiss Federal Office of Energy SFOE

Energy Research and Cleantech

Final report dated 24.03.2020

# High-efficiency power converters for potentially-large energy-savings applications

Source: © Copyright POWERlab-EPFL 2019

**Date:** 24 March 2020

**Location:** Bern

**Subsidiser:**

Swiss Federal Office of Energy SFOE

Energy Research and Cleantech Section

CH-3003 Bern

[www.bfe.admin.ch](http://www.bfe.admin.ch)

**Subsidy recipients:**

Ecole Polytechnique Fédérale de Lausanne (EPFL)

EPFL-STI-IEL-POWERlab

Building ELD

Station 11

CH-1015 Lausanne

<http://powerlab.epfl.ch/>

**Authors:**

Prof. Elison Matioli, director of the POWERlab-EPFL, [elison.matioli@epfl.ch](mailto:elison.matioli@epfl.ch)

Dr. Georgios Kampitsis, POWERlab-EPFL, [georgios.kampitsis@epfl.ch](mailto:georgios.kampitsis@epfl.ch)

**SFOE project coordinators:**

SFOE head of domain: Michael Moser, [michael.moser@bfe.admin.ch](mailto:michael.moser@bfe.admin.ch)

SFOE programme manager: Roland Brüniger, [roland.brueniger@r-brueniger-ag.ch](mailto:roland.brueniger@r-brueniger-ag.ch)

**SFOE contract number:** SI/501568-01

**All contents and conclusions are the sole responsibility of the authors.**

## Zusammenfassung

Ziel dieses Projekts ist es, Stromrichterschaltungen mit großem Energieeinsparpotenzial für anspruchsvolle Anwendungen wie PV-Mikrowechselrichter und LED-basierte Straßenbeleuchtung zu entwerfen und zu demonstrieren. Diese Arbeit zeigt nicht nur das volle Potenzial der bei Powerlab-EPFL entwickelten Technologien, sondern ermöglicht auch eine enge Beziehung zu den Branchen. Dieses Projekt ermöglicht in Kombination mit der einzigartigen Struktur unseres Labors eine Optimierung sowohl auf der Geräte- als auch auf der Schaltkreisseite, da die Informationen aus den Schaltkreisen als Feedback zur Optimierung der Geräte und umgekehrt verwendet werden können. Dieser Ansatz eröffnet eine neue Ära für Leistungselektronikanwendungen und das aktuelle Projekt hat dazu beigetragen, unsere Arbeit zu beschleunigen, zu demonstrieren und zu kommunizieren. Der erste Teil dieses Projekts war der Identifizierung der Wandertopologie gewidmet, die die vorteilhaften Eigenschaften der lateralen GaN-HEMTs am besten ausnutzt. Wir haben einen modularen 2,5-kW-Switched-Capacitor-Multilevel-Wandler ohne magnetische Komponenten entworfen und entwickelt, der nur 0,2 L Volumen einnimmt. Dieses System wurde später auf eine neue PV-Architektur angewendet, die auf der Parallelschaltung mehrerer PV-Module auf der Hochspannungsseite dieser Wandler basiert. Unser Ansatz hilft dabei, den Energieverlust im Zusammenhang mit teilweiser Verschattung anzugehen. Um die Leistungsdichte des Prototyps des magnetfreien Wandlers zu maximieren, haben wir ein neuartiges mikrofluidisches Kühlsystem entwickelt, das auf reinraumgefertigten Si-Kühlplatten basiert und für maximale Leistungszahlen optimiert ist. Auf Bauteilebene haben wir eine hochskalierte Tri-Anode-GaN-Schottky-Barrier-Diode hergestellt und den ersten monolithisch integrierten Vollbrückengleichrichter und passiven Spannungsvervielfacher in einer Cockcroft-Walton-Konfiguration demonstriert. Letztendlich hat unsere Arbeit in diesem Projekt die Grenzen der Konvertertechnologie erweitert, indem alle vorteilhaften Eigenschaften von Materialien mit großer Bandlücke ausgenutzt wurden.

## Résumé

Le but de ce projet est de concevoir et de démontrer des circuits de conversion d'énergie offrant un potentiel important d'économie d'énergie dans des applications exigeantes, telles que les micro-onduleurs photovoltaïques et l'éclairage public à LED. Ces travaux illustrent non seulement le potentiel des technologies créées au Powerlab-EPFL, mais facilitent également les relations étroites avec les industries. Ce projet, associé à la structure unique de notre laboratoire, permet une optimisation à la fois du côté dispositif et du côté circuit. Les informations provenant des circuits peuvent notamment être utilisées comme rétroaction pour optimiser les dispositifs et inversement. Cette approche ouvre une nouvelle ère pour les applications en électronique de puissance et le projet en cours a permis d'accélérer, de démontrer et de communiquer notre travail. La première partie de ce projet visait à identifier la topologie de convertisseur qui exploite au mieux les caractéristiques avantageuses des GaN HEMT latéraux. Nous avons conçu et mis au point un convertisseur multiniveau modulaire à condensateur commuté de 2.5 kW sans composant magnétique qui occupe seulement 0.2 L de volume. Ce système a ensuite été appliqué à une nouvelle architecture PV basée sur la connexion en parallèle de plusieurs modules PV du côté haute tension de ces convertisseurs. Notre approche permet de réduire la perte d'énergie liée à l'ombrage partiel. Afin de maximiser la densité de puissance du prototype de convertisseur sans magnétique, nous avons développé un nouveau système de refroidissement microfluidique, basé sur des plaques froides en Si fabriquées en salle blanche et optimisé pour un coefficient de performance maximal. Au niveau des appareils, nous avons fabriqué une diode à barrière Schottky à trois anodes GaN mise à l'échelle et avons présenté le premier redresseur en pont complet et multiplicateur de tension passifs intégrés monolithiquement dans une configuration Cockcroft-Walton. Finalement, notre travail dans le cadre de ce projet a repoussé les limites de la technologie du convertisseur en exploitant toutes les propriétés avantageuses des matériaux à large bande interdite.

## Summary

The purpose of this project is to design and demonstrate power converter circuits with large energy saving potential in demanding applications, such as PV microinverters and LED-based street lighting. Not only does this work showcases the full potential of the technologies created at Powerlab-EPFL, but also facilitates a close relationship with industries. This project, in combination with the unique structure of our Lab, enables optimization in both the device and circuit sides, as the information from circuits can be used as feedback to optimize the devices and vice-versa. This approach opens a new era for power electronics applications and the current project helped fast-track, demonstrate and communicate our work. The first part of this project was dedicated to identify the converter topology that best exploits the advantageous characteristics of the lateral GaN HEMTs. We designed and developed a 2.5kW switched capacitor modular multilevel converter with no magnetic components that occupies only 0.2L of volume. This system was later applied to a new PV architecture based on the parallel connection of multiple PV modules at the high-voltage side of these converters. Our approach helps address the energy loss related to partial shading. To maximize the power density of the magnetic-free converter prototype, we developed a novel microfluidic cooling system, based on clean-room fabricated Si cold plates and optimized for maximum coefficient of performance. In a device level, we fabricated a scaled up Tri-anode GaN Schottky Barrier Diode and demonstrated the first monolithically integrated full bridge rectifier and passive voltage multiplier in a Cockcroft-Walton configuration. Ultimately, our work within this project pushed the limits of the converter technology by exploiting all advantageous properties of wide band-gap materials.

## Main findings

- Development of a new ultra-compact and efficient magnetic-less DC/DC converter with high step-up conversion ratio and low cooling requirements. The developed system has huge potential of entering the market related to renewable energy generation, electric vehicles and data centre applications.

- Utilization of the developed magnetic-free converter in a module-level PV architecture in parallel-configuration for maximum power extraction under partial shading conditions. The new PV configuration is capable of increasing up to 20% the annual energy yield of residential PV systems in urban areas with low installation height.

- Development of a compact and energy-efficient cooling system based on multiple miniaturized microfluidic cold-plates compact through a 3D-printed flow distribution manifold. This novel approach offers a new way of co-engineering the cooling and the electronics together to achieve more compact and efficient power converters.

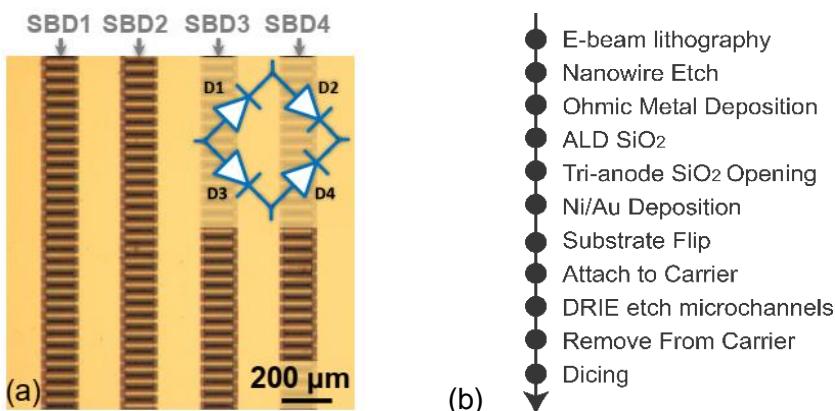

- Demonstration of the first monolithically integrated GaN full bridge rectifier and an 8-time GaN voltage multiplier in a Cockcroft-Walton configuration, utilizing the Tri-Anode GaN Schottky Barrier Diodes (SBDs), developed in our Lab.

# Contents

|                                                                                       |           |

|---------------------------------------------------------------------------------------|-----------|

| <b>ABBREVIATIONS .....</b>                                                            | <b>6</b>  |

| <b>1 INTRODUCTION .....</b>                                                           | <b>7</b>  |

| 1.1 BACKGROUND INFORMATION.....                                                       | 7         |

| 1.2 PURPOSE OF THE PROJECT .....                                                      | 8         |

| 1.3 OBJECTIVES .....                                                                  | 8         |

| <b>2 PROCEDURES AND METHODOLOGY .....</b>                                             | <b>9</b>  |

| <b>3 RESULTS AND DISCUSSION .....</b>                                                 | <b>11</b> |

| 3.1 GAN-BASED MICRO-CONVERTERS FOR MAXIMUM ENERGY EXTRACTION FROM PV GENERATORS ..... | 12        |

| 3.1.1 <i>Voltage Multiplied PV Architecture</i> .....                                 | 12        |

| 3.1.2 <i>Modelling and Simulations</i> .....                                          | 14        |

| 3.1.3 <i>Experimental Evaluation</i> .....                                            | 18        |

| 3.1.4. <i>Real-time maximum power point tracking</i> .....                            | 21        |

| 3.1.4 <i>Discussion and Future Work</i> .....                                         | 22        |

| 3.2 THERMAL MANAGEMENT .....                                                          | 23        |

| 3.2.1 <i>Modelling, Design and Fabrication</i> .....                                  | 23        |

| 3.2.2 <i>Experimental Evaluation</i> .....                                            | 29        |

| 3.2.3 <i>Full System Testing</i> .....                                                | 33        |

| 3.2.4 <i>Cooling Systems Comparison</i> .....                                         | 34        |

| 3.2.5 <i>Discussion and Future Work</i> .....                                         | 35        |

| 3.3 MINIATURIZATION OF POWER CONVERTERS.....                                          | 36        |

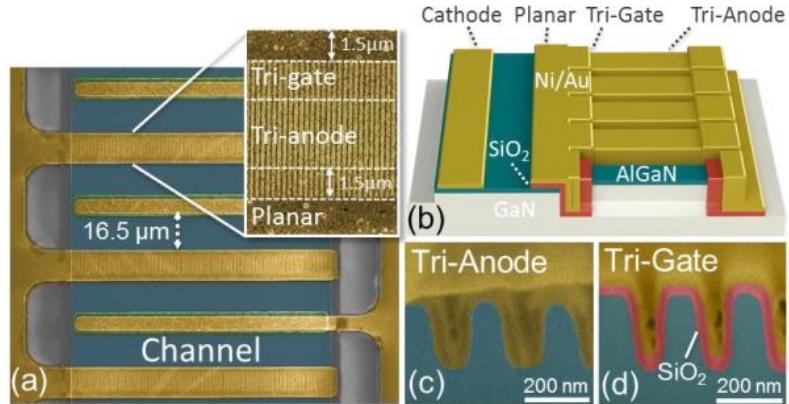

| 3.3.1 <i>Development of a GaN Tri-Anode Schottky Barrier Diode</i> .....              | 36        |

| 3.3.2 <i>Monolithically integrated Full Bridge Rectifier</i> .....                    | 39        |

| 3.3.3 <i>Monolithically integrated Voltage Multiplier</i> .....                       | 42        |

| 3.4 AUTONOMOUS LED STREET-LIGHT PROJECT.....                                          | 43        |

| 3.4.1 <i>The Solar Panel</i> .....                                                    | 43        |

| 3.4.2 <i>Energy storage</i> .....                                                     | 46        |

| 3.4.3 <i>Circuit Design</i> .....                                                     | 47        |

| 3.4.4 <i>Online Connectivity</i> .....                                                | 50        |

| 3.4.5 <i>Data Acquisition – Server</i> .....                                          | 54        |

| 3.4.6 <i>Demonstration</i> .....                                                      | 55        |

| <b>4 CONCLUSIONS .....</b>                                                            | <b>56</b> |

| <b>5 OUTLOOK AND NEXT STEPS.....</b>                                                  | <b>57</b> |

| <b>6 NATIONAL AND INTERNATIONAL COOPERATION .....</b>                                 | <b>57</b> |

| <b>7 COMMUNICATION .....</b>                                                          | <b>57</b> |

| <b>8 PUBLICATIONS .....</b>                                                           | <b>58</b> |

| <b>9 REFERENCES .....</b>                                                             | <b>59</b> |

## Abbreviations

|             |                                    |                |                                     |

|-------------|------------------------------------|----------------|-------------------------------------|

| <b>2DEG</b> | Two-dimensional electron gas       | <b>MSB</b>     | Most significant bit                |

| <b>AGM</b>  | Absorbed glass mat                 | <b>NOCT</b>    | Nominal operation cell temperature  |

| <b>BMS</b>  | Battery management systems         | <b>P&amp;O</b> | Perturb and Observe                 |

| <b>CAD</b>  | Computer-aided design              | <b>PCB</b>     | Printed circuit board               |

| <b>CNC</b>  | Computer numerical controlled      | <b>PI</b>      | Proportional Integral               |

| <b>COP</b>  | Coefficient of Performance         | <b>PLL</b>     | Phase locked loop                   |

| <b>DER</b>  | Distributed energy resources       | <b>PR</b>      | Proportional-resonant               |

| <b>DI</b>   | Deionized                          | <b>PS</b>      | Partial shading                     |

| <b>DOD</b>  | Depth of discharge                 | <b>PV</b>      | Photovoltaic                        |

| <b>DPT</b>  | Double pulse tester                | <b>PVPO</b>    | PV power optimizers                 |

| <b>FBR</b>  | Full Bridge Rectifier              | <b>PWM</b>     | Pulse width modulation              |

| <b>FOB</b>  | Focused ion beam                   | <b>SBD</b>     | Schottky Barrier Diode              |

| <b>FRB</b>  | Fast-recovery diode                | <b>SEM</b>     | Scanning electron microscope        |

| <b>HEMT</b> | High Electron Mobility Transistor  | <b>SLA</b>     | Stereolithography                   |

| <b>IC</b>   | Integrated circuit                 | <b>SoC</b>     | State of charge                     |

| <b>ICP</b>  | Inductively coupled plasma         | <b>SOGI</b>    | Second-order generalized integrator |

| <b>IR</b>   | Infrared                           | <b>SP</b>      | Series-Parallel                     |

| <b>LED</b>  | Light emitting diode               | <b>SS</b>      | Subthreshold swing                  |

| <b>LPF</b>  | Low-pass filter                    | <b>TCT</b>     | Total cross-tied                    |

| <b>LSB</b>  | List significant bit               | <b>TCTR</b>    | TCT rearranged                      |

| <b>MCU</b>  | Microcontroller unit               | <b>TIM</b>     | Thermal interface material          |

| <b>MLPE</b> | Module-level power electronics     | <b>VMPV</b>    | Voltage multiplied Photovoltaic     |

| <b>MMC</b>  | Manifold microchannel              | <b>VRLA</b>    | Valve regulated lead-acid           |

| <b>MMCC</b> | Modular multilevel capacitor clamp | <b>ZCS</b>     | Zero current switching              |

| <b>MPPT</b> | Maximum power point tracking       |                |                                     |

# 1 Introduction

## 1.1 Background information

In this project all of the defined goals were met and the milestones summarized in Table 1 have been surpassed. A short description of the different aspects of the project is given in this section and a detailed explanation is presented later in this report.

| Milestones                                                                  | Sept 2017 | 2018 | 2019 | March 2020 |

|-----------------------------------------------------------------------------|-----------|------|------|------------|

| M1: Design and Efficiency comparison of soft- and hard-switching topologies |           |      |      | ▲          |

| M2: Demonstration of initial circuits for LED-street lighting               |           |      | ▲    |            |

| M3: Design and demonstration of initial circuits for PV micro-inverters     |           |      | ▲    |            |

| M4: Integration of full prototype                                           |           |      |      | ▲          |

| M5: Feedback to our devices and circuit re-design                           |           |      |      | ▲          |

| M6: Final prototype design and demonstration                                |           |      |      | ▲          |

| M7: Technology transfer to companies involved                               |           |      |      | ▲          |

| M8: Final report                                                            |           |      |      | ▲          |

Table 1. Milestones

For the 1<sup>st</sup> Milestone, *Design and Efficiency comparison of soft- and hard-switching topologies*, we investigated new switching capacitor topologies, both with transistors and diodes, for high power density applications. First, we examined a modular multilevel capacitor clamped (MMCC) DC/DC converter with a 10-times voltage boost capability and soft switching operation, achieved by tuning the switching frequency to match the internal resonant frequency. We then proceeded with the investigation of a diode-based switching capacitor topology that utilizes the state-of-the-art monolithically integrated diodes developed in POWERLab. For efficient implementation of this part of the project, there was a close collaboration between the circuit design and the device fabrication teams, in accordance with the Milestone 5, *Feedback to our devices and circuit re-design*.

We also fulfilled the 6<sup>th</sup> Milestone, *Final prototype design and demonstration*, regarding the PV micro-inverters. We utilized the developed MMCC converter to boost the output voltage of a PV panel by 10 times, an approach that enables the parallel connection of all the PV modules at the common high-voltage DC-Bus. We demonstrated that our new PV architecture can have better conversion efficiency (>96%) and significantly higher power extraction efficiency (>99.7%) compared to state-of-the-art topologies, while the parallel connection addresses all issues related to partial shading.

We also moved forward with the 4<sup>th</sup> Milestone, *Integration with full prototype*, by optimizing the new microchannel liquid cooling heatsinks, dedicated to the micro-inverter prototypes. A thorough mathematical analysis was performed to find the optimum microchannel width that result to the best coefficient of performance at minimum flow rate and pressure drop. We developed an aluminum milled and a 3D printed heatsink that incorporate the clean-room fabricated microchannel cold-plates to assess the performance of our novel cooling system. The results show by co-designing the electronics with an efficient cooling system we can reduce the thermal resistance of the heatsink by one order of magnitude.

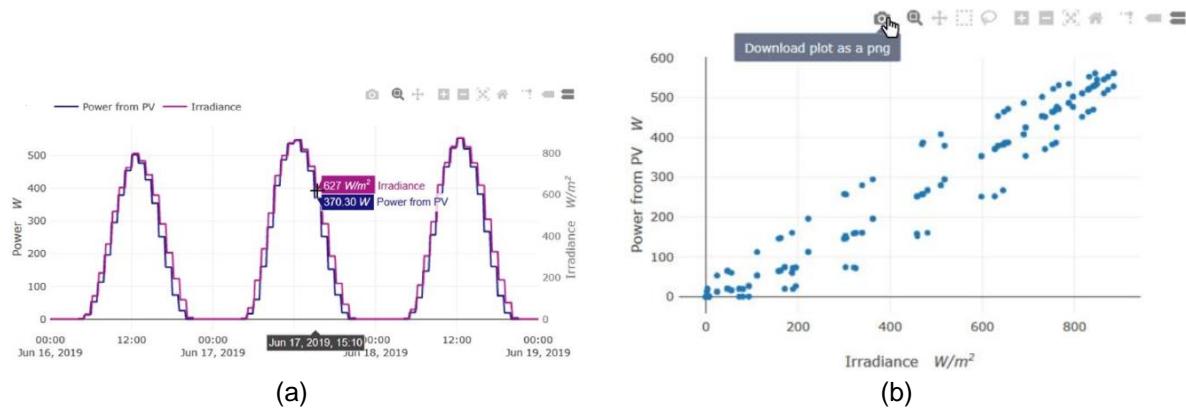

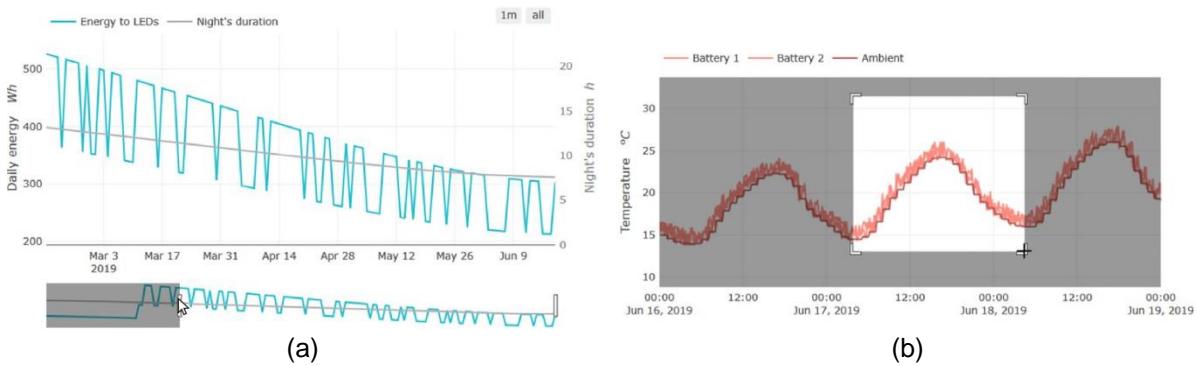

We have also completed the *Final prototype design and demonstration* of the *circuit for LED-street lighting* (Milestones 4<sup>th</sup> and 2<sup>nd</sup> and 3<sup>rd</sup>). We completely redesigned the entire system to achieve a long lifetime, reliability and low cost. We revisited both the energy storage system and the PV module. We also developed an online human interface environment for storing and managing useful data, such as produced and consumed power, battery temperature, local environmental conditions and more.

Finally, this report is the realization of the last Milestone, *Final report*, which includes noteworthy outcomes of our research, reveals our approach to disseminate our results in high-impact factor journals and international conferences and proposes ideas for a successful continuation of our work.

## 1.2 Purpose of the project

The main purpose of this project is to design and demonstrate power converter circuits that will be part of a full demonstrator for two main applications: PV microinverters and LED-based street lighting. This project is complementary to the SFOE-funded project: “GaN-based Power Electronics for Energy Efficiency Applications”, however the present project aims to focus on the conclusions obtained in this first SFOE project to develop real-size demonstrators. This not only showcases the full potential of the technologies created at Powerlab-EPFL, but facilitates a close relationship with industries. The final goal of this project was to develop and transfer these technologies to the industry, which in our view is the only way for our technologies to reach their full societal impact.

This project is strongly related to our current activities, since in our long-term our goal is to deploy the designed and fabricated devices in our laboratory. This gives an extra degree of freedom for optimization in both the device and circuit sides, as the information from circuits can be used as feedback to optimize the devices and vice-versa. In addition, other circuit components have also been re-designed (as the high frequency of GaN devices allows the reduction of parasitic inductive and capacitive components, and their high temperature operation reduces the need for cooling systems). This is in particular relevant for magnetic components, which can be much reduced in size under high frequency with a judicious design. This allowed the demonstration of more efficient systems with much reduced footprint.

## 1.3 Objectives

The main objective of this project was to demonstrate optimum converter topologies with co-designed cooling systems that fully exploit the potential of GaN technology. To reach this goal, we addressed several scientific and practical challenges. More specifically, the layout of the magnetic-free converter had to be carefully designed to overcome all electromagnetic interference (EMI) issues, related to the Miller effect and driver-to-transistor physical distance. At the same time, maximizing the power density of the converter increases the heat fluxes, which in turn makes the heat extraction a challenging task. To this end, we needed to come up with an efficient liquid cooling system with high coefficient of performance, low pressure drop and low flow rate requirements. Additionally, equal distribution of the coolant to all GaN devices needed to be ensured for a reliable operation. Another goal of the project was to apply the magnetic free converters in a PV application with large energy saving potential. In this field, we addressed the issues related to the parallel connection of multiple nX converters on the same high voltage DC bus and, more specifically, the reverse current flow formed by the switched capacitors current loops. Also, to maximize power extraction capability of the PV generator, even in non uniform insolation conditions, we had to transfer all control functionalities in a secondary conversion stage (inverter / regulated dc/dc converter), while retaining low control complexity. Finally, to achieve system miniaturization we addressed the challenges of monolithic integration of several power devices on the same substrate. The first objective was to scale up (in current) our SBDs and, then, solve the problems related to the common-buffer leakage. Ultimately, our work resulted in novel approaches for combining electronics, cooling and device fabrication.

## 2 Procedures and methodology

This project has been the enabling factor for the development of methods of power conversion with large energy saving potential. Our main goal was to push the limits of power density of the state-of-the-art converter by exploiting one of the most interesting characteristics of the GaN technology: i.e. the lateral structure of the GaN HEMTs that offers the possibility to monolithically integrate several devices in a single power integrated circuit (IC). This feature opens a new era for power electronics applications and the current project helped fast-track, demonstrate and communicate our work.

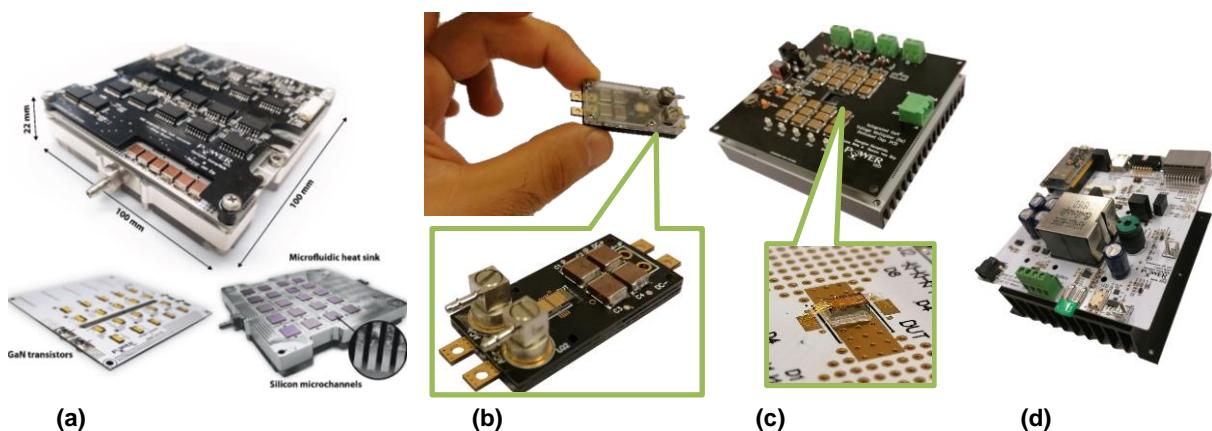

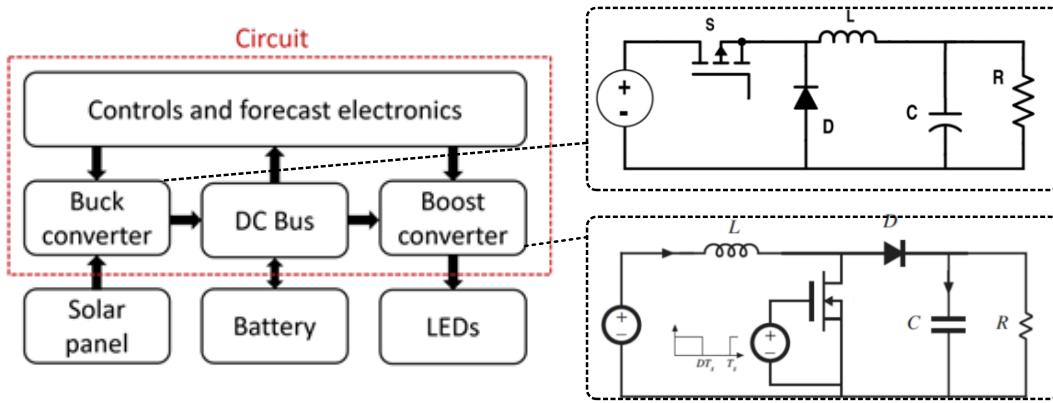

The work started with the introduction of a new ultra-compact and efficient magnetic-less DC/DC converter, shown in Figure 1(a), suitable for photovoltaic (PV) systems (but also for electric vehicles, data centers and DC microgrids) that eliminates all magnetic components, which commonly dominate the size and weight of power systems. The transistor technology also helped migrate from bulky and unreliable electrolytic capacitors to efficient, compact and long-lifetime multilayer ceramic capacitors. We optimized the circuit by developing a detailed model of a single cell (2x conversion ratio) and running simulations in Matlab/Simulink.

We took full advantage of the exceptional performance of the magnetic free converter by introducing a module-level PV architecture in parallel-configuration for maximum power extraction, under partial shading (PS) conditions (**Section 3.1**). The nX converter is intended to boost the PV voltage by a fixed ratio, while the maximum power point tracking MPPT is shifted to the grid-side inverter. Although simple, this approach has not been tested before. We connected the voltage-multiplied PV modules (VMPV) in parallel to a common DC-bus, which offers expandability to the system and eliminates the PS issues of a typical string architecture. Our approach relieves the PV-side converter from bulky capacitors, filters, controllers and voltage/current sensors, allowing for a compact and efficient conversion stage. We initially simulated the new configuration in a 5 kW residential PV system and compared against conventional PV arrangements. For the experimental validation, we tested the VMPV architecture on a 2-module 500 WP prototype, exhibiting an excellent power extraction efficiency of over 99.7% under PS conditions and minimal DC-bus voltage variation of 3%, leading to a higher total system efficiency compared to most state-of-the-art configurations.

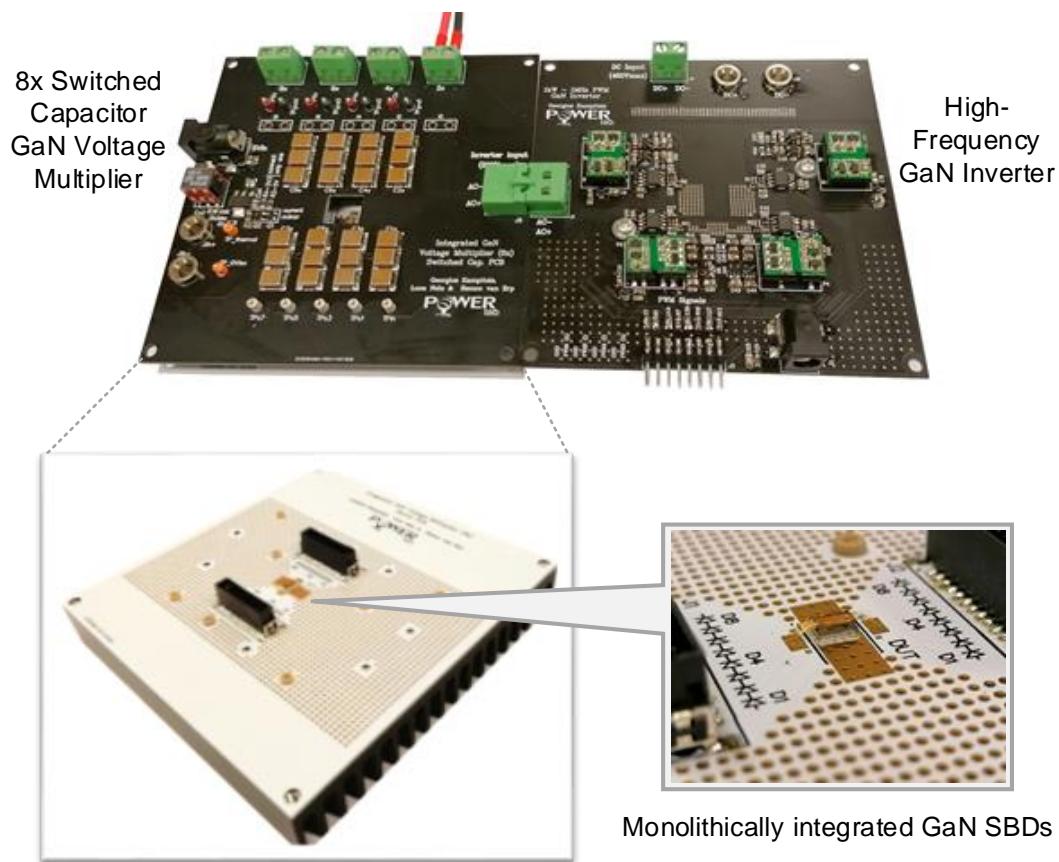

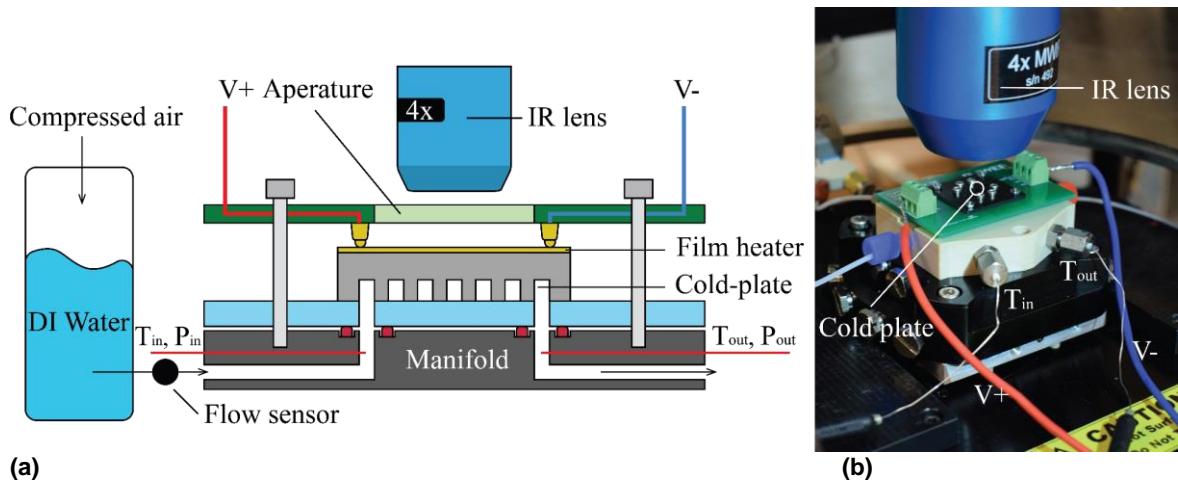

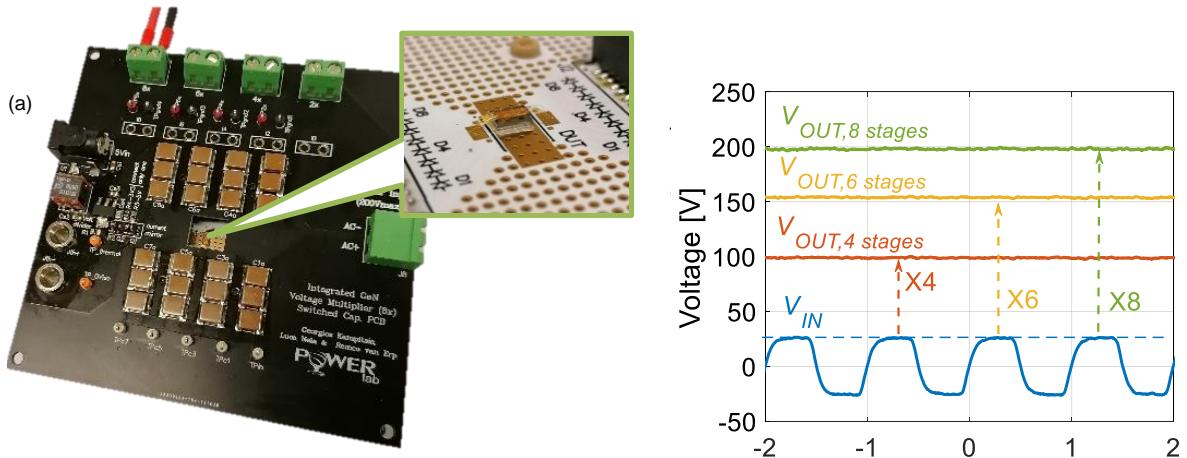

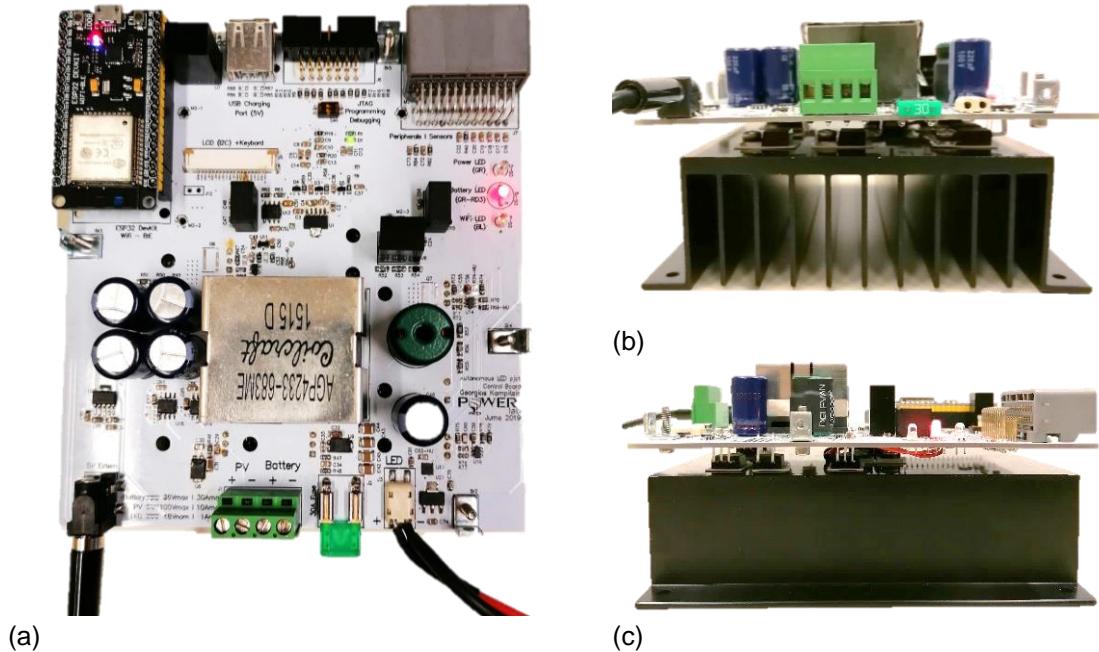

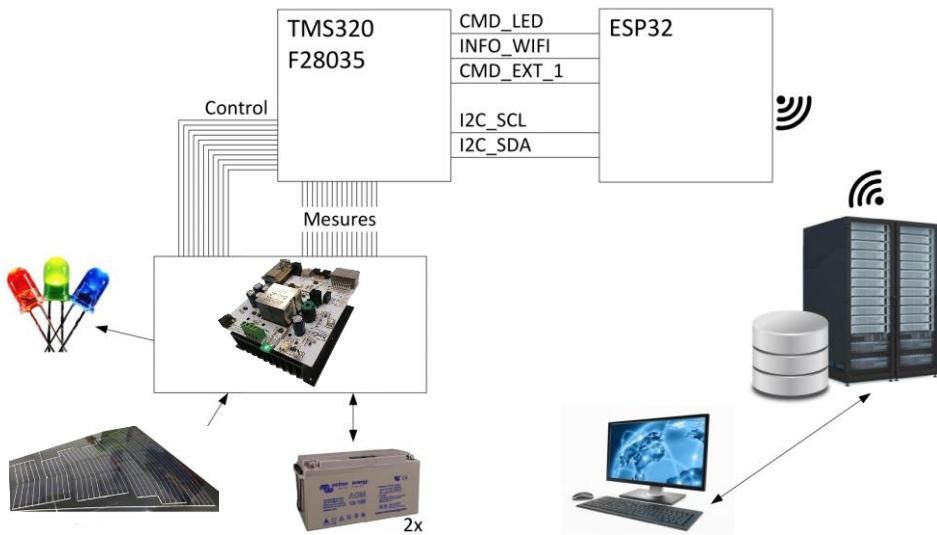

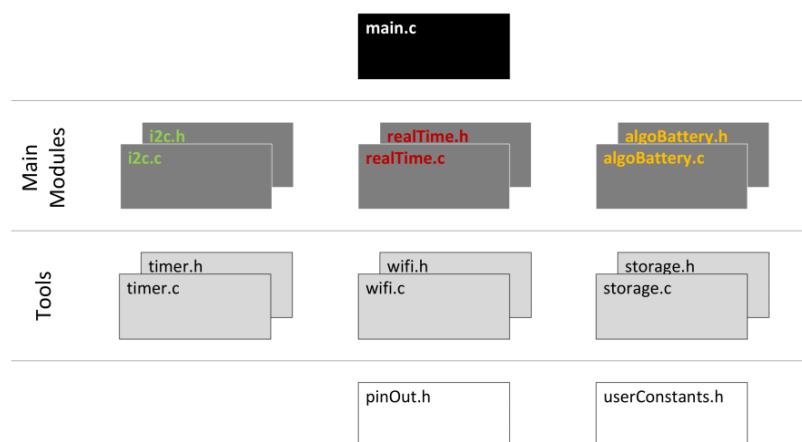

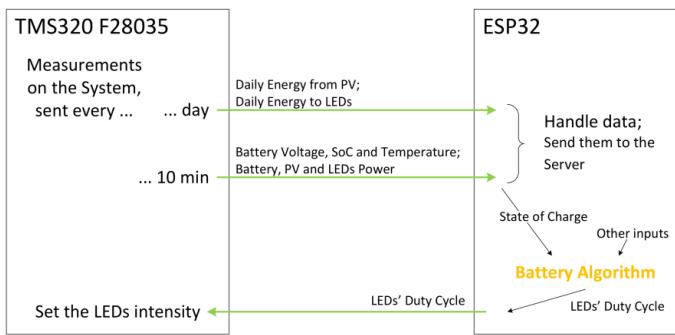

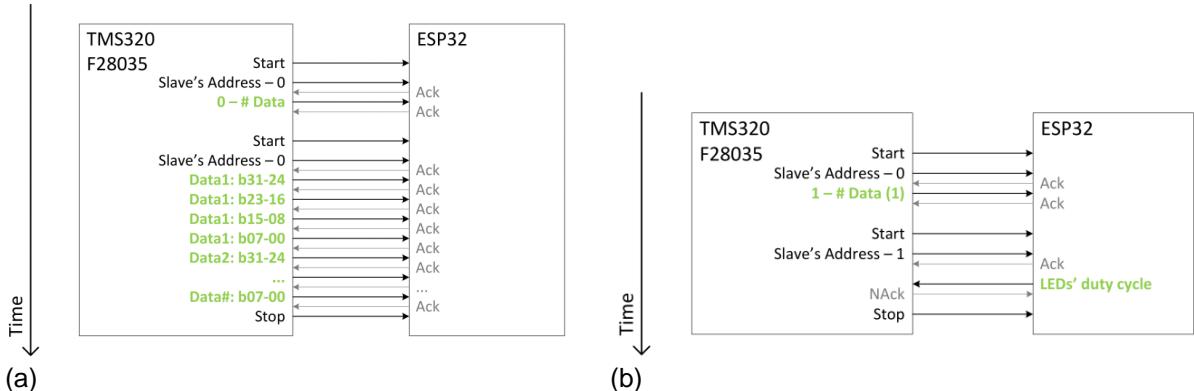

Figure 1: (a) High power density GaN-based magnetic-free converter with co-designed micro-fluidic cooling system. (b) Monolithically integrated full-bridge rectifier of 120W with embedded microchannels and liquid distribution system (c) 8x voltage multiplier with monolithically integrated SBDs (d) New MPP tracker for the autonomous street lighting system. It features WiFi and Bluetooth connectivity for collective valuable information on a server.

To optimize the heat extraction capability of our new converter, we developed a new approach for compact and energy-efficient cooling, where multiple miniaturized microfluidic cold-plates are attached to the transistors, as depicted in Figure 1(a). We minimized the high pressure drop associated with microchannels by connecting these cold-plates in parallel using a compact 3D-printed flow distribution manifold. In **Section 3.2** we present the modeling, design, fabrication and experimental evaluation of this microfluidic cooling system and provide a design strategy for achieving energy-efficient cooling with minimized pumping power. A thermal resistance of 0.2 K/W was measured at a flow rate of 1.2 ml/s and a pressure drop of 600 mbar, enabling the cooling of a total of 300 W of losses in the converter using only 75 mW of pumping power, which can be realized with small micropumps. Experimental results show a 10-fold increase in power density compared to conventional cooling, potentially up to 30 kW/l. Our cooling approach offers a new way of co-engineering the cooling and the electronics together to achieve more compact and efficient power converters.

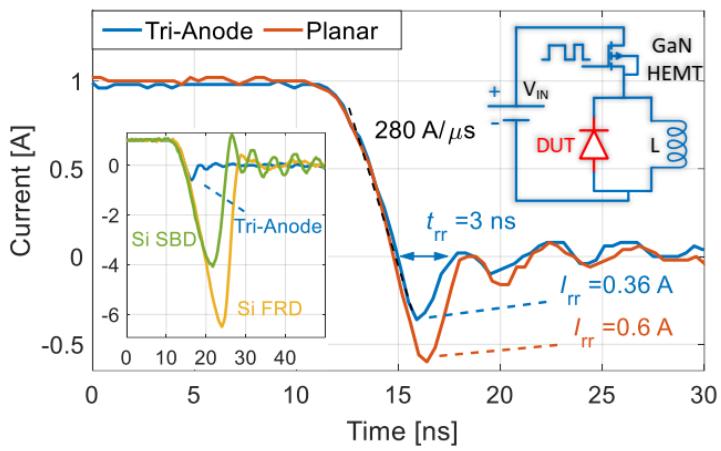

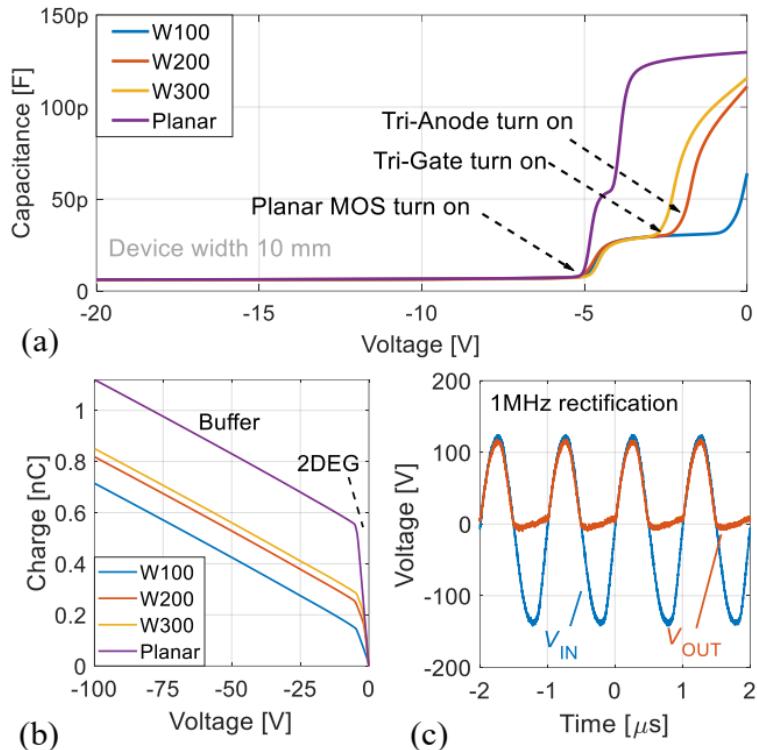

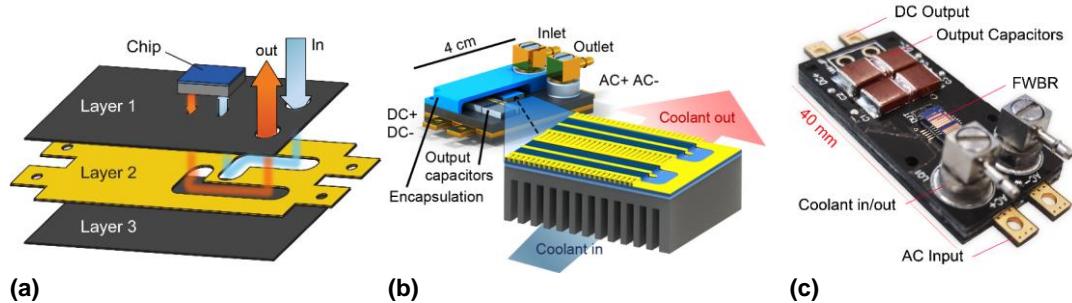

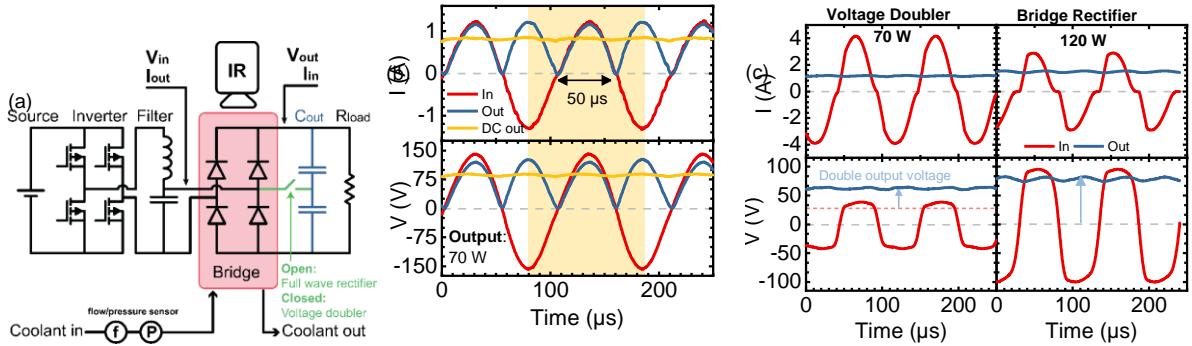

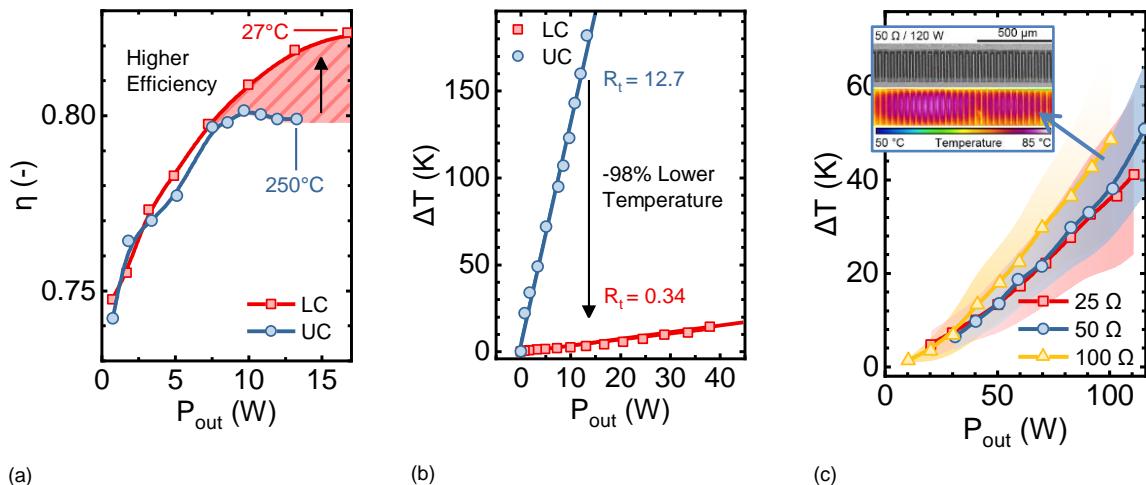

Having demonstrated a fully functional magnetic-free converter and its cooling system, we moved forward miniaturizing the system by integrating several devices on the same chip. This step was revolutionary, both for our lab and the research community, since it requires the expertise for several different disciplines (material science, electrical engineering, mechanical engineering). As a first demonstrator we developed a full bridge rectifier, shown in Figure 1(b), utilizing the Tri-Anode GaN Schottky Barrier Diodes (SBDs), developed in our Lab. As explained in **section 3**, our SBDs show excellent DC performance with low turn-on voltage and large breakdown thanks to their 3D contact structure around the two-dimensional electron gas (2DEG) channel. More importantly, though, they exhibit remarkable dynamic performance, proven by the substantial decrease in the recovery charge and an improvement in frequency response. In the same context of integrating several GaN SBDs on the same chip, we demonstrated the first GaN voltage multiplier in a Cockcroft-Walton configuration, illustrated in Figure 1(c), where 8 scaled-up diodes constitute the core of a 70W 8-time voltage boost converter.

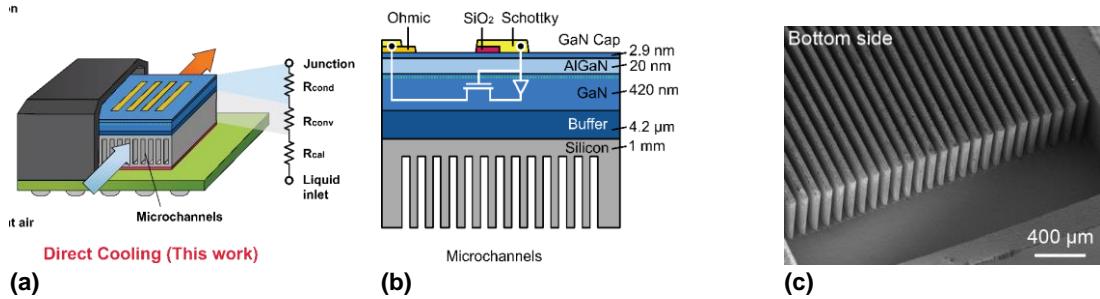

We also expanded our knowledge on the microfluidic cooling systems and developed a new direct-cooling system for GaN-on-Si power integrated circuits (ICs), in which the silicon substrate functions as a microfluidic heat sink, turning Si into a cost-effective, high thermal performance substrate. Flowing coolant through microchannels etched in the backside of the substrate enables a much denser integration of GaN power devices in a single chip. A novel hybrid printed circuit board (PCB) was also developed (see Figure 1(b)) that provides fluidic and electric connection to the liquid-cooled power IC. We believe that the high cooling efficiency, large heat extraction capabilities and low-cost fabrication process of embedded microchannels on GaN-on-Si, in combination with new PCB based coolant delivery, can be an enabling technology for the next generation of ultra-high power-density ICs.

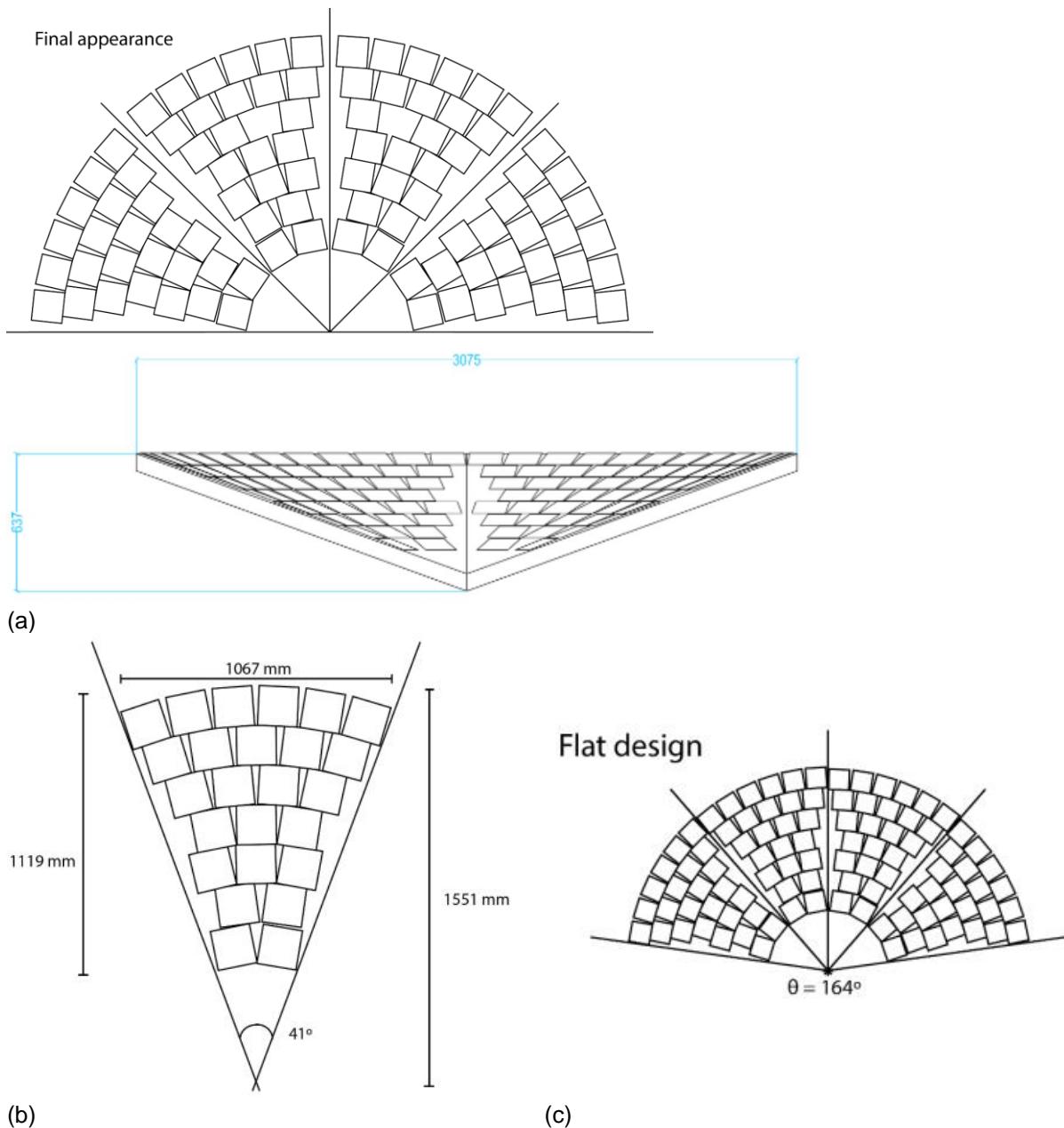

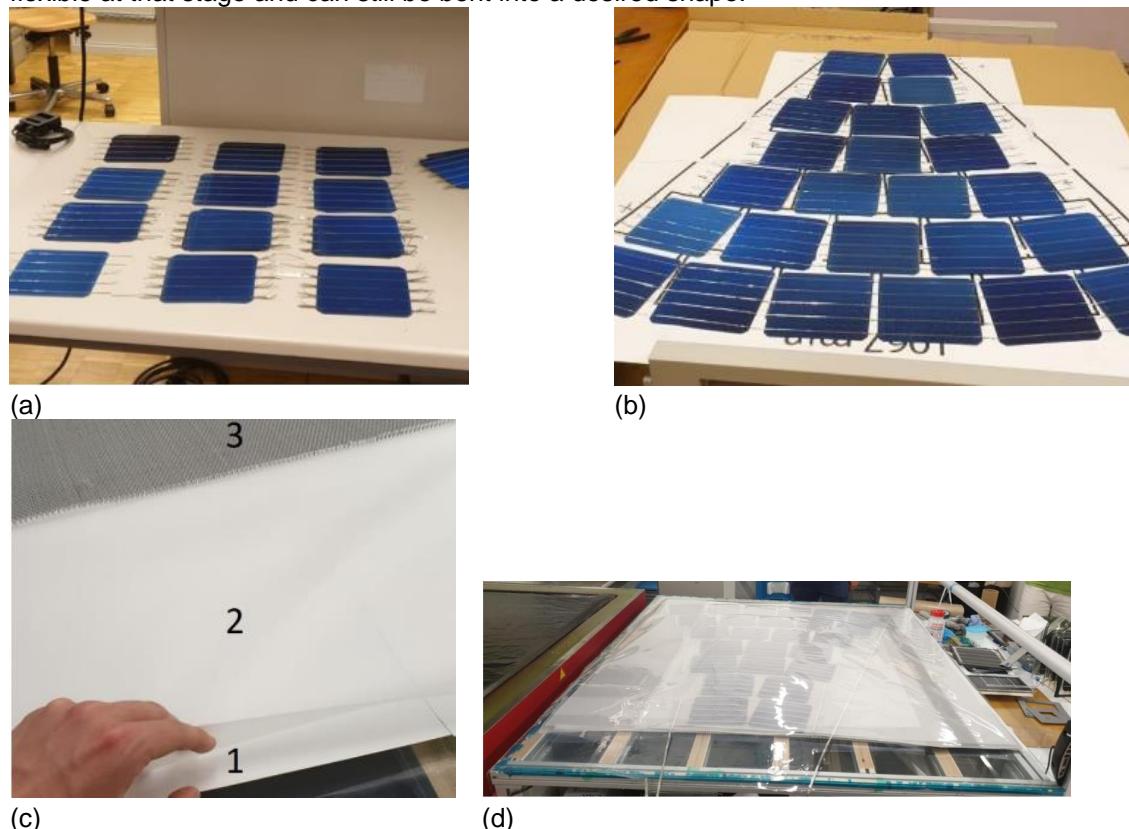

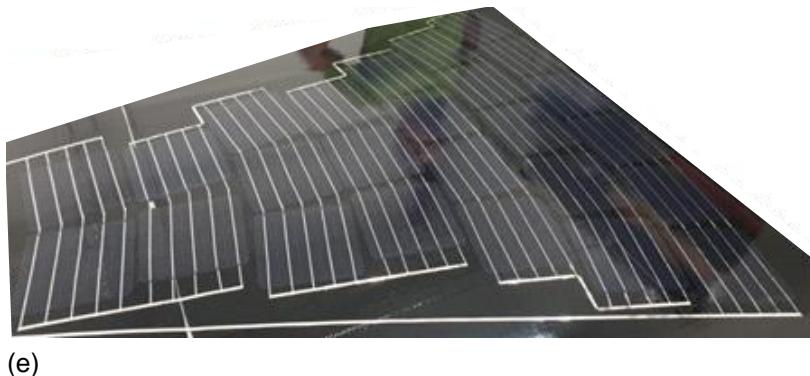

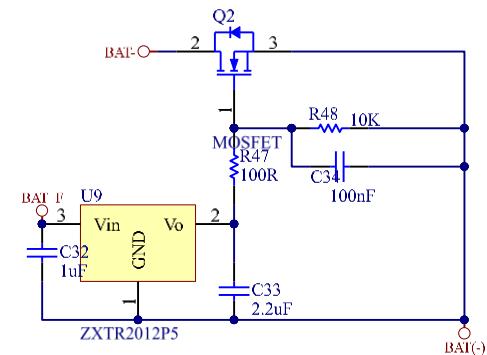

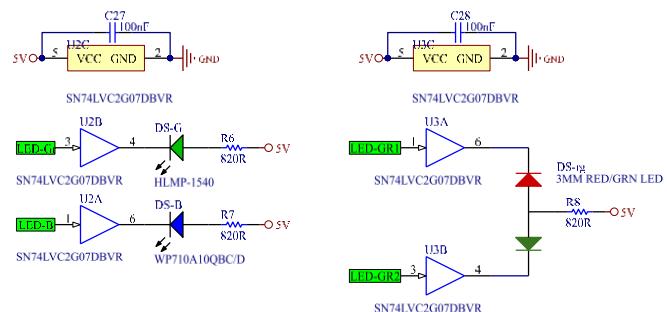

We also revisited the autonomous LED street lighting system to finalize its design and add features for enhancing the system-to-human interface. We collaborated with a team of architects that designed a custom PV panel that is aesthetically appealing and has the electrical requirements specified by this application. Gel lead-acid batteries replaced the old LiFePo4, given that weight is not a restriction to the system and they can perform way more reliable in low temperature conditions. A completely new MPP tracker, shown in Figure 1(d), was designed and developed that incorporates both the battery charger and the LED driver in a single PCB. The system also features WiFi connectivity that helps upload important statistical data, such as environmental conditions, produced energy, consumed energy, etc., on an online server. Final a graphical user interface was developed to present the stored data in a representative form.

### 3 Results and discussion

Throughout this project, we have achieved the following, summarizing results:

1. **Demonstration of a new PV architecture based on the magnetic-free micro-converters:** We have revisited the topologies used in conventional energy conversion systems for PV applications and have proposed a completely new PV arrangement. We utilize a high power density magnetic-free nX converter with each PV panel to form a high voltage module and then connect them in parallel, effectively addressing the partial shading issues. The flat efficiency curve of the nX converter, combined with the outstanding power extraction efficiency of the parallel architecture is estimated to increase the energy yield up to 20% in residential PV systems.

2. **Optimization of the new near-junction microfluidic heatsinks:** We developed customized clean room fabricated Si-based microchannels and liquid spreading manifolds that can effectively cool down the local hotspots of modern GaN-based power converters. These heatsinks were used to cool down the developed converters utilizing both commercial transistors but also our Lab's GaN devices. We designed and developed two liquid distribution manifolds, one aluminum milled and a 3D printed, that equally distribute the coolant to all hotspots. We optimized the cooling system by performing a detailed mathematical analysis, supported by 3D finite element simulations.

3. **Demonstration of state-of-the-art devices fabricated in our laboratory:** We have developed extremely fast GaN Schottky barrier diodes with high breakdown voltages (>600V), ultra-low leakage current and negligible reverse recovery charge. Our devices performance well surpasses all other commercial diodes of any technology (Si or SiC). To fully exploit the advantageous features of our devices we demonstrated scaled-up diodes with a current capability >2A.

4. **Monolithic integration of our devices to form power ICs:** We integrate several of our novel SBDs in a single chip to form high power ICs. We first developed a full bridge rectifier and tested it up to 120W. The system was cooled-down through our established microchannel cooling system and a liquid distribution integrated in the PCB. Our latest achievement concerns the fabrication of an 8x integrated voltage multiplier in Cockcroft-Walton configuration, tested up to 70W. This prototype is one step closer to the magnetic-free converter concept and showed promising potential for the future power ICs.

5. **A complete redesign of the autonomous street lighting system:** We updated the entire system (including the energy storage system, the PV module, the MPPT tracker), while considering reliability and cost as the main criteria for this practical applications. We collaborated with a team of architects that designed a practical and, at the same time, aesthetically appealing PV generator, the construction of which was performed in EPFL, Microcity Lab. We also developed a database for storing useful information of the autonomous LED light (produced and consumed power environmental conditions and more), through WiFi communication protocol. We finally built a graphical user interface to present the data in a concise and representative manner.

6. **Established new collaborations and obtained extra funding to help the execution of the project:** In addition to the grants that we have for the complementary projects including the SNSF projects, ERC Starting Grant, SNSF Assistant Professor Energy Grant, European Space Agency (ESA), which focus on new technologies to scale up our devices for the applications related to this project. This project was a major enabler for us to establish collaboration with large European companies and laboratories, through an European Union H2020 ECSEL projet (UltimateGAN), which awarded 48M Euros for 26 partners in Europe. This project is enabling a close collaboration of our laboratory with the semiconductor company Infineon. In addition, we are currently establishing collaboration projects with other large semiconductor and power companies such as ABB and Eaton. We have also established collaborations with a Swiss company (Aebischer & Bovigny) to design and fabricate automated lighting systems. We have also established collaborations with a Swiss company Montena to design high-power pulse generator systems.

These achievements are described more in details below:

### 3.1 GaN-Based Micro-Converters for Maximum Energy Extraction from PV Generators

#### 3.1.1 Voltage Multiplied PV Architecture

Photovoltaics (PV) are increasingly gaining grounds over other power generation technologies, conventional or renewables, and are expected to dominate in future distributed energy resources (DER) and smart grid applications [1]. This trend is supported by the latest statistics, according to which the PV capacity installation in 2017 surpassed all other technologies, for the first time in history [2]. However, maximum energy extraction from the PV generator is commonly hindered due to partial shading (PS) conditions. This is particularly sever in urban environments, with low installations height. According to [7]–[9], PS is responsible for a reduction of the annual energy yield by 10-20% in building integrated PVs.

To increase the PV energy production under PS conditions, various software and hardware solutions have been proposed over the last decades. Although economical and easily applicable, software solutions, such as enhanced maximum power point tracking (MPPT) algorithms [3] [4], can only have a limited impact, since the shaded modules will still be bypassed or will operate at sub-optimum power point. On the contrary, hardware solutions can offer a significant improvement in PV generation during PS. More specifically module-level power electronics (MLPE) is the most effective hardware solution for PS loss mitigation. This approach aims to maximize the power yield of each individual panel through dedicated MPPTs.

In this field, micro-inverter topologies have proven commercially successful, since they offer the flexibility to connect any number of PV modules directly to the AC grid [5], but they exhibit low power density, due to the large component count and strict filter requirements [6]. Other popular MLPE alternatives include the PV power optimizers (PVPO) [7], distributed power processors [8] and voltage equalizers [9], which are buck-boost DC-DC converters, integrated with the solar panels of a typical string arrangement. According to [10], these systems have lower long-term efficiency compared to micro-inverters and reduced expandability, due to the minimum required string length [11]. The state-of-the-art approach promotes *micro-converters* that allow parallel connection of the PV modules in a single DC-bus, through high step-up DC-DC converters [26]. This solution aims to exploit the clear advantages of parallel-configuration for addressing PS effects [27]. Several converter topologies with large voltage boost ratio have lately been proposed, including cascade boost [26], coupled inductors [28], switching capacitors [29], and combinations of the above. However, these topologies are known to require complicated control algorithms and, most importantly, employ electrolytic capacitors and magnetic components that limit the power density and the lifetime of the system. They also exhibit significant efficiency drop in low loading conditions, which is a drawback, given that a PV generator operates within 30%-80% of its nominal power for 80% of the time [34].

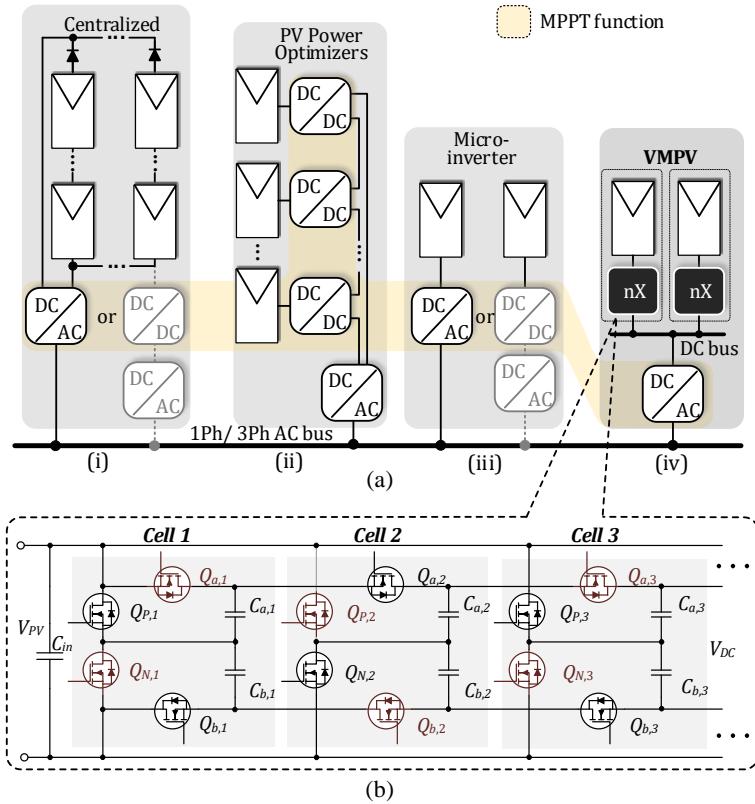

**Our goal is to successfully address the PS issues and overcome the limitations of the conventional converters and, by utilizing the highly efficient and compact nX converter, already developed within this project in PowerLab.** The foundation of the new approach relies on the combinations of a non-regulated high-step-up micro-converter with each PV panel, to form a high-voltage/low-current building block. All the Voltage Multiplied PV (VMPV) modules are connected in parallel at the input of the grid-side inverter, which simultaneously regulates the operating point of all PV panels with a central MPPT. Each module contributes additively to the total system output by injecting the power that corresponds to the common DC-voltage, i.e.  $P_{PV-j}(V_{PV-j} = V_{DC}/n)$ , where  $P_{PV-j}$  and  $V_{PV-j}$  are the output power and voltage, respectively, of the  $j$  panel. A simplified schematic of the proposed VMPV architecture is presented in Figure 2 (a, topology iv).

Figure 2: (a) PV architectures: i) central inverter, ii) PVPOs iii) micro-inverters and iv) the Voltage Multiplied architecture. The highlighted area indicates the converters responsible for the MPPT. (b) Schematic diagram of the magnetic-free SC voltage amplifier.

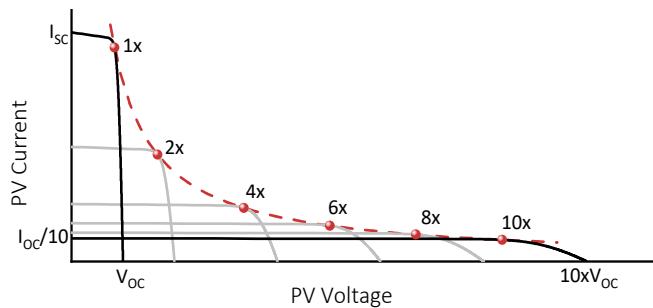

The effect of the PV module voltage amplification can be viewed as “stretching” the output I-V characteristic to higher voltages and lower currents, while keeping the produced power constant, as shown in Figure 3. The multiplication factor,  $n$ , should be higher than the  $V_{DC}/V_{MP}$  ratio, where  $V_{DC}$  is the required DC-link voltage for grid integration (e.g. 400 V) and  $V_{MP}$  is the nominal PV panel voltage at MPP (e.g. 40 V).

Figure 3: Modified I-V characteristic of the voltage multiplied PV module.

### PV-Side Converter

As demonstrated in the 2018 annual report “*High-efficiency power converters for potentially-large energy-savings applications*”, the nX converter combines high power density with high conversion efficiency and a fixed voltage ratio. The fixed boost ratio is not a limitation for this application, given that the maximum power point (MPP) voltage of a PV panel varies insignificantly with the environmental conditions. It should be mentioned here that the increased efficiency and power density of the nX converter come at a cost of a high transistor count. However, the latest advancements on GaN technology reveal the unique potential for monolithic integration of multiple devices on a single power chip [12], rendering this topology an ideal platform for future VMPV modules.

Our approach offers control simplicity, since all power devices are switching in a complementary pattern with a fixed 50 % duty cycle. There is no need for feed-back control loop thus, no requirements for voltage/current sensors, costly microcontrollers and communication links. A simple pulse width modulation (PWM) integrated circuit (IC) is adequate for the operation of this converter.

The power devices are subjected to low voltage and current stress, due to the modular structure of the topology. Further, the converter can operate in zero current switching (ZCS) mode, if the switching frequency is tuned to match the circuit resonance frequency, determined by the capacitors and the circuit parasitic inductances [13].

The utilization of state-of-the-art wide bandgap GaN transistors offer the option to replace the electrolytic capacitors of the circuit, which is the most common point of failure [5], [6], [14], with robust and efficient ceramic capacitors, by increasing the switching frequency of operation. This technology migration helps to achieve a long lifetime for the converter, to match that of the solar panels (above 25 years), which is an important requirement for modern PV systems. The small footprint and low driving requirements of HEMTs further contribute to the miniaturization of the micro-converter.

### Gris-Side Inverter

Regulation of the operating point of a PV module, string or system is traditionally performed by the front-end converter, as indicated by the highlighted area in Figure 2(a – topologies *i-iii*). In this study, the fixed voltage ratio at the PV-side requires that the MPPT function is performed by the grid-side inverter, much like a single-stage system. Therefore, although our topology is fundamentally a two-stage system, it operates like a single-stage centralized system in terms of MPPT function, but with higher MPP tracking efficiency. Specifically, the merits of this new architecture are:

- The entire PV system has always a single MPP, even under mismatched irradiance and temperature conditions, due to the parallel connection of the VMPVs. As a result, no PV module is bypassed and the MPP is always successfully tracked, as opposed to the multi-peak P-V curves in centralized architectures, leading to almost 100% power extraction efficiency under any partial shading conditions.

- The DC-link voltage variation is limited due to the inherently small deviation of VMP with the environmental conditions. This makes it easy for the inverter to extract the maximum power while meeting the input voltage requirements, in contrast to single-stage systems under PS.

- Having a single grid-side inverter permits implementation of sophisticated control functions, such as ancillary services to the grid (e.g., fault ride through, reactive power injection, frequency regulation), as opposed to the micro-inverters that cannot afford such complexity.

#### 3.1.2 Modelling and Simulations

Here we aim to assess the power extraction efficiency of the new PV architecture under PS conditions, against conventional PV configurations, through simulations in Matlab/Simulink. We define

the total system efficiency,  $\eta_{sys}$ , as the product of conversion efficiency,  $\eta_c$ , and extraction efficiency,  $\eta_{ext}$ :

$$\eta_{sys} = \eta_c \cdot \eta_{ext} \quad (1)$$

$\eta_{ext}$  is given as the ratio of the average output power of the PV system to the total available power from all individual modules. Reduction of  $\eta_{ext}$  is usually attributed to 3 factors: (a) the shaded modules operate at a sub-optimal operating point or are completely bypassed, (b) the MPPT is trapped on a local MPP and (c) the MPPT causes oscillations around the normal operating point. For a fair comparison of the VMPV with other conventional architectures, the first factor will be considered, assuming that the MPPT algorithm can always find the global maximum, even in the case multiple power peaks at PS.

### Shading Patterns

We consider two realistic shading patterns, depicted in Figure 4. Solid lines show the SP configuration and dashed lines represent the TCT interconnection scheme.

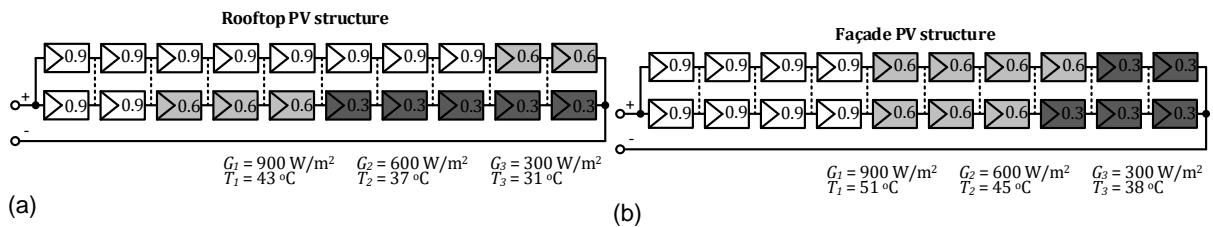

#### 1) Shading Pattern A: Long-Narrow

In this case the shadow covers the majority of one string of a rooftop PV structure, giving rise to three irradiance intensity levels,  $G_1 = 900 \text{ W/m}^2$ ,  $G_2 = 600 \text{ W/m}^2$  and  $G_3 = 300 \text{ W/m}^2$  as shown in Figure 4 (a). Ambient temperature of  $20^\circ\text{C}$  and wind speed of  $1 \text{ m/s}$  are considered, according to the international standard IEC-61215. The nominal operation cell temperature (NOCT) is also included in Figure 4, considering both the photoelectrical and photothermal conversion effect.

#### 1) Shading Pattern B: Short-Wide

This scenario concerns a façade PV system, partially shaded by the pattern illustrated in Figure 4(b). In contrast to an open rack rooftop structure, the building integrated PVs are characterized by a higher temperature, since only one side of the panel is in contact with the air.

Figure 4: Indicative PS scenarios. (a) Long-narrow shading pattern A and (b) Short-wide shading pattern B.

### Static Characteristics

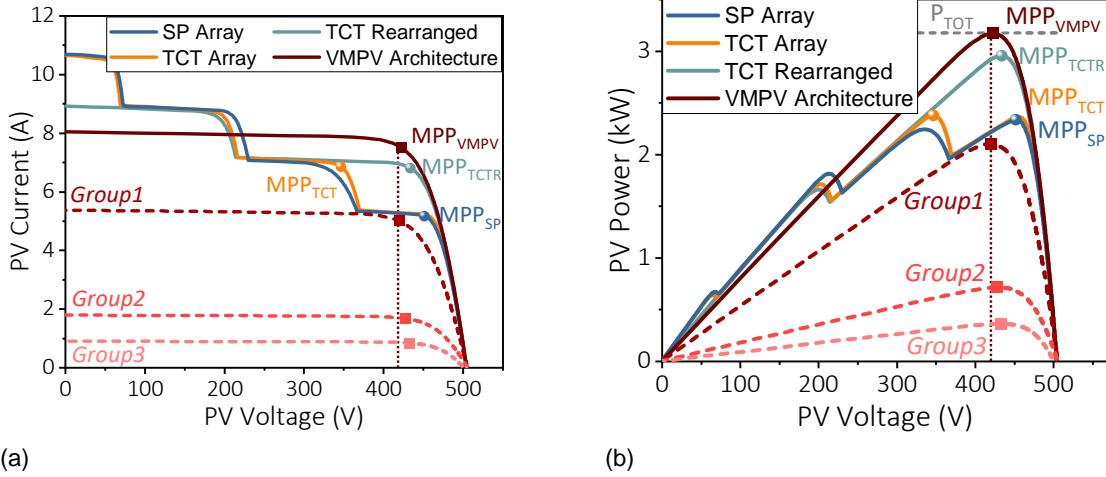

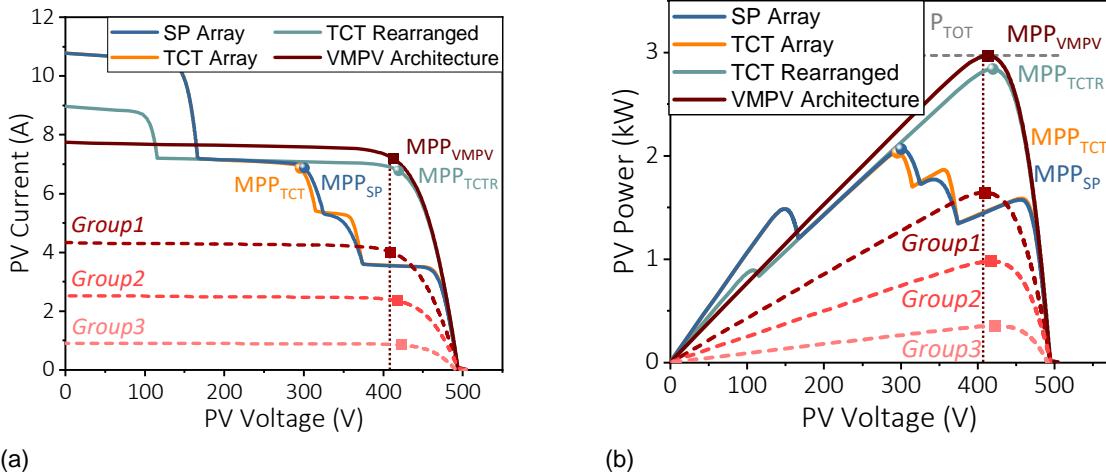

The simulation results for the case-study A are presented in Figure 5. The grey dashed line corresponds to the maximum available power,  $P_{TOT}$ , extracted from an ideal PV architecture and is used as a benchmark in the comparison ( $\eta_{ext} = 100\%$ ). It is evident that both SP and TCT configurations exhibit poor extraction efficiencies of 73.59% and 74.94%, respectively, due to the bypassing of the shaded modules. On the other hand, the dynamic rearrangement of the panels significantly improves the efficiency to 93.12% and reduces the number of local maxima to 2. However, it is our VMPV architecture that achieves the best extraction efficiency of 99.86% with just a single global MPP.

To further investigate these numbers, the  $I$ - $V$  and  $P$ - $V$  curves of the individual modules are shown in Figure 5, classified into three groups (Group 1-3) according to the three different operating conditions. In contrast to SP and TCT (static or rearranged), the high-voltage parallel connection ensures that all PV groups operate at a common voltage (vertical dotted line) that is very close to the individual MPPs (square markers). It is worth noting that even for the highly shaded Group 3, more than 99.5% of the available power is extracted.

Figure 5: (a) *I-V* and (b) *P-V* curves of the examined PV architectures under the *shading pattern A: Long-Narrow*. The figure also includes the output characteristics of the 3 PV groups of the proposed parallel connected VMPV system that correspond to the different irradiance levels.

The output I-V and P-V characteristics for the *shading pattern B* are presented in Figure 6. Even under these highly non-uniform irradiance and temperature conditions the VMPV architecture still exhibits a near-perfect efficiency of 99.8%. As a comparison, the SP and TCT interconnection schemes have  $\eta_{ext}(SP) = 69.4\%$  and  $\eta_{ext}(TCT) = 68.3\%$ , respectively, while the electrically rearranged TCT array has  $\eta_{ext}(TCTR) = 95.5\%$ .

Figure 6: (a) *I-V* and (b) *P-V* curves of the examined PV architectures under the *shading pattern B: Short-Wide*. The figure also includes the output characteristics of the 3 PV groups of the proposed parallel connected VMPV system that correspond to the different irradiance levels.

### Real-time maximum power point tracking

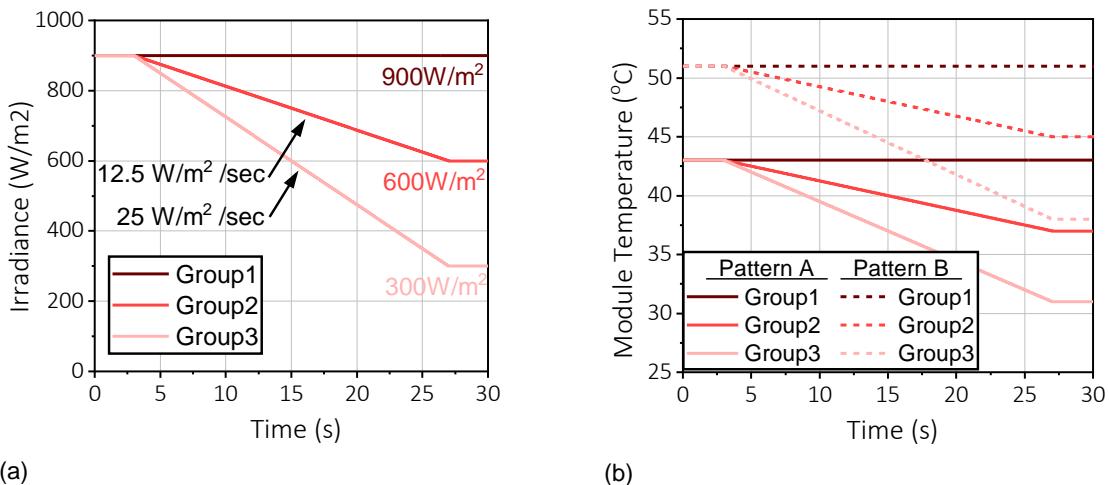

To evaluate the time-response of the whole system under variation of the atmospheric conditions, the proposed PV architecture is connected to a single-phase grid-side inverter. The scenario where a façade PV structure is initially uniformly insolated ( $G_1 = 900 \text{ W/m}^2$ ) and gradually shaded to match *shading pattern B* is simulated. A linear drop of the irradiance is considered (see Figure 7), at a rate of  $25 \text{ W/m}^2$  per second, which is a representative value for rapidly changing environmental conditions. The temperature variation of the individual PV groups is shown in Figure 7 (b), for the investigated *patterns B*.

Figure 7: (a) Irradiance and (b) temperature variation with time for the 3 PV groups of the VMPV architecture. Continuous line represent the *shading pattern A* and dashed line is used for the *shading pattern B*.

The inverter control is structured in three nested control loops, as in [15]. The outer control loop is a Perturb and Observe (P&O) MPPT that is applied at the common high-voltage DC-bus and produces the reference DC-voltage,  $V_{DC}^*$ . In the middle control loop, a proportional-integral (PI) controller regulates the active and reactive power reference to be injected to the grid,  $P^*$  and  $Q^*$ , respectively. A proportional-resonant (PR) current controller is implemented in the inner control loop, while the grid frequency is extracted by a second-order generalized integrator phase locked loop (SOGI - PLL).

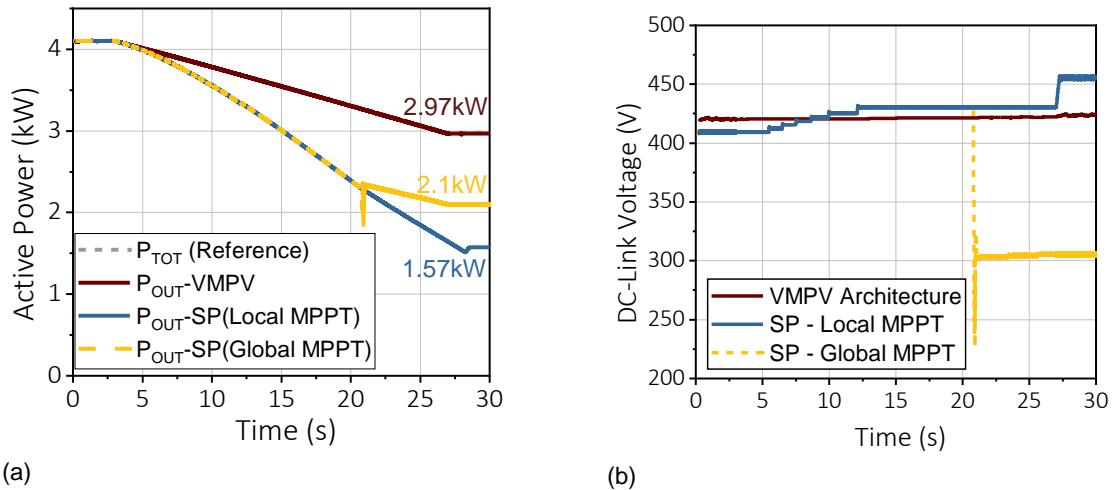

Figure 8 shows the power and voltage variation of the proposed VMPV and standard SP architectures when the shading evolves towards *shading pattern B*. The new VMPV architecture, follows closely the benchmark curve, even when all the shaded panels have reached their steady state conditions (Time  $> 27 \text{ s}$ ). This scenario highlights the merits of a single MPP in the proposed parallel connection against the multiple peak formation in conventional SP configurations and the challenges in identifying the global one. Even if a sophisticated MPPT algorithm is employed that always converges to the global MPP (yellow dashed curves), the respective DC-link voltage (300V in Figure 8(b)) may be outside the inverter limits, thus not allowing operation at the MPP, leading to even lower extraction efficiency.

Figure 8: (a) Active power fed to the grid and (b) DC-link voltage variation with time for the proposed VMPV under *shading pattern B*.

The simulation results show that the proposed VMPV architecture combines the best of MLPE and centralized topologies: it yields near-optimal power extraction (like MLPE, in contrast to the centralized) while allowing for sophisticated control functions in the inverter (like centralized, as opposed to micro-inverters).

### 3.1.3 Experimental Evaluation

#### Setup and shading scenarios

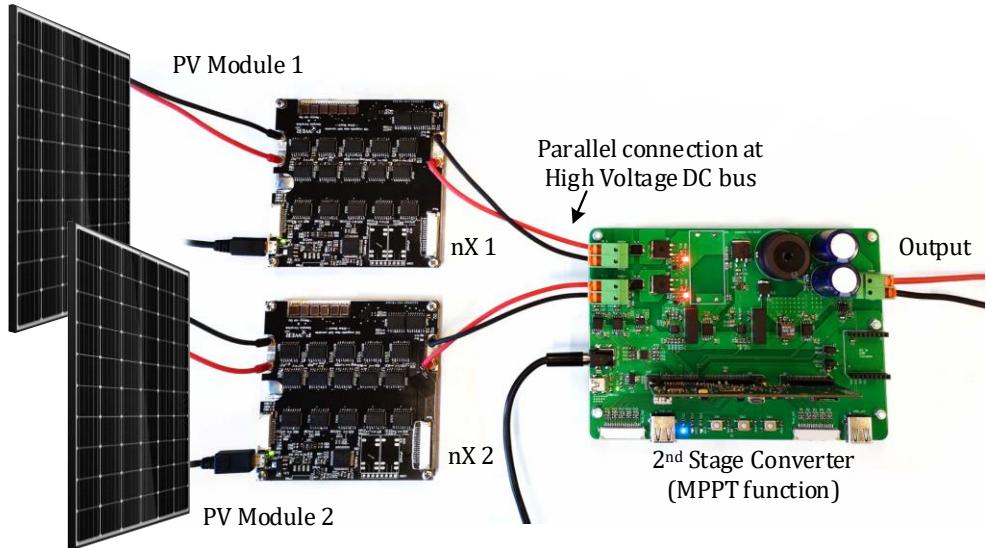

In order to experimentally assess our new PV architecture, two 245 WP PV modules of the same type VBHN245SJ25 are used as inputs to two nX converters that are connected in parallel at the high-voltage side, as depicted in Figure 9. Throughout the experiment, both PV panels are placed close to each other on a structure of fixed inclination with respect to the horizon. A semi-transparent fabric is used to cover one PV module completely and uniformly to emulate PS conditions.

A DC-DC converter that performs all control functions, including scanning of the PV curves and MPPT, feeding a resistive load was used as a simple substitute of the grid-tied inverter. This setup allows safe and repetitive testing of the new architecture, while the results are also valid for the grid-connected system. The switching frequency of the buck converter was set to 20 kHz and the MPPT period to 250 ms. All voltage and current measurements were continuously monitored with a sampling rate of 4 kSamples/s and then filtered via a digital low-pass filter (LPF) with a cutoff frequency of 100 Hz to reject the switching noise. The key components and parameters of the experimental setup are summarized in TABLE II.

Figure 9: Experimental setup consisting of two identical PV modules along with their 10X voltage multipliers, a secondary-stage converter performing the MPPT function feeding a resistive load.

TABLE II

List of Components of the Experimental Setup

| Component                              | Parameter                          | Value          |

|----------------------------------------|------------------------------------|----------------|

| PV Modules                             | Part Type                          | VBHN245SJ25    |

|                                        | $V_{MP}$                           | 44.3V          |

|                                        | $I_{MP}$                           | 5.53A          |

|                                        | $V_{OC}$                           | 53V            |

|                                        | $I_{SC}$                           | 5.86A          |

| Module -level nX converter             | Transistors in $Q_{P/N}$ position  | GS61008T       |

|                                        | Transistors in $Q_{a/b}$ position  | GS66508T       |

|                                        | Switching Capacitors               | 4x2.2uF, X6S   |

|                                        | Gate Driver                        | LM5114         |

|                                        | Digital/Power Isolator             | ISOW7842F      |

| 2 <sup>nd</sup> -stage DC-DC converter | Series Diodes                      | S10KC          |

|                                        | $L_{DC-DC}$                        | 1.5 mH         |

|                                        | $C_{DC-DC}$                        | 50 $\mu$ F     |

|                                        | Transistor                         | IPB65R190CFD   |

|                                        | Switching Diode                    | C3D08065E      |

|                                        | Microcontroller                    | TMS320F28379D  |

|                                        | Switching Frequency ( $F_{SW-B}$ ) | 20 kHz         |

|                                        | MPPT period ( $T_{MPPT}$ )         | 250 ms         |

|                                        | Voltage/Current sampling rate      | 4 ksamples/s   |

|                                        | LPF cutoff frequency ( $F_o$ )     | 100 Hz         |

| Output Resistor                        | $R_{out}$                          | 0-240 $\Omega$ |

### Static Characteristics

The  $I$ - $V$  and  $P$ - $V$  characteristics of the proposed PV system were recorded in two shading patterns: A) uniform irradiance and temperature conditions and B) partial shading, where one panel is uniformly shaded while the other one remains unshaded. The curves are captured by slowly changing the operating point within 5 sec (scanning).

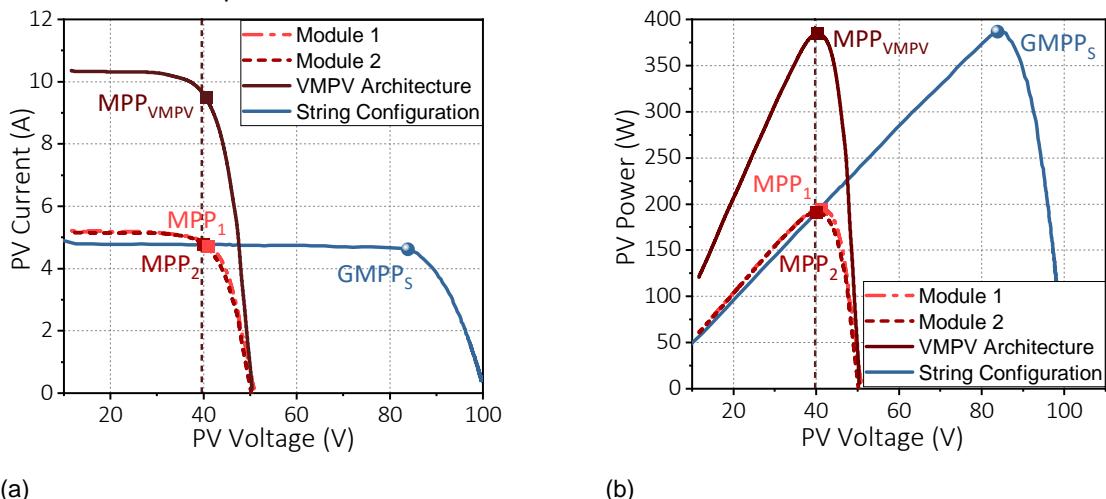

Figure 10 shows the characteristic curves of the two individual PV modules (dashed and dash-dotted lines) and the combined curve of the proposed VMPV architecture (solid red line), under uniform irradiance and temperature conditions. The two modules are not identical and their MPPs (MPP1 and MPP2) differ by 3.4 W and are spaced by 1.17 V. However, the power loss of the VMPV approach is just 0.4 W, resulting in an excellent extraction efficiency of 99.9%. In fact, both modules operate at 99.9% of their respective MPPs.

(a)

(b)

Figure 10: Experimentally extracted (a)  $I$ - $V$  and (b)  $P$ - $V$  characteristics of the PV modules under the *shading pattern A*: uniform irradiance and temperature conditions. Values were measured at the PV side for both VMPV and string architectures.

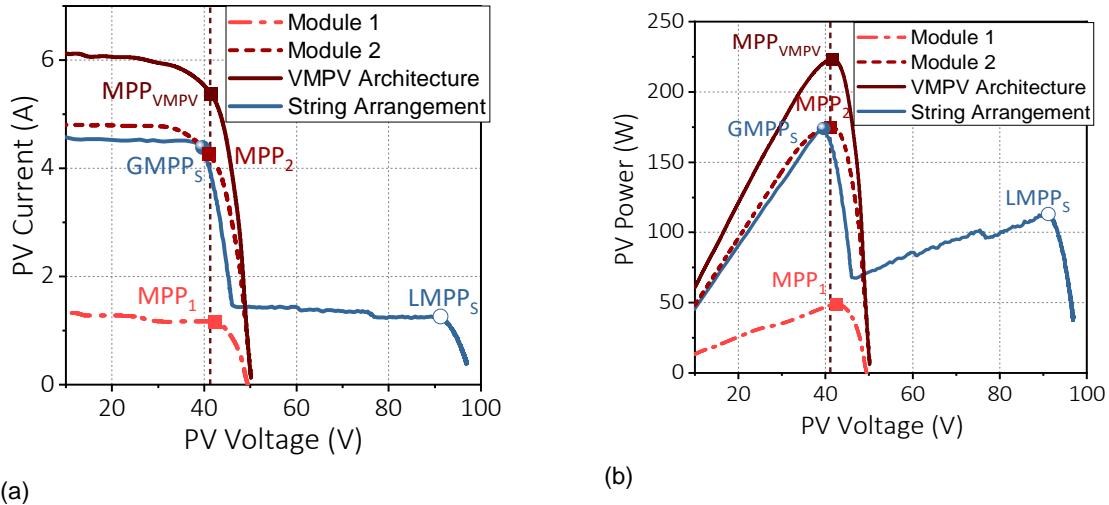

Figure 11 shows the experimentally extracted  $I$ - $V$  and  $P$ - $V$  traces under the *Shading Pattern B*: Module 1 is entirely shaded, while Module 2 remains unshaded. Although  $P_{PV}(MPP1) = 48.7$  W is more than 3.5 times smaller than  $P_{PV}(MPP2) = 174.9$  W, their respective voltage difference is just 1.45 V. That leads to an extraction efficiency of 99.74% for the VMPV system. On the other hand, the global MPP of the series connection is  $P_{PV}(GMPPS) = 174$  W, equal to MPP2 minus the power dissipated at the bypass diode of Module 1, resulting in an extraction efficiency of just 77.8%. Still, it is highly possible that a simple MPPT algorithm would converge at a local MPP (LMPP), in which case half of the PV power would be lost ( $\eta_{ext}(LMPPS) = 50.5\%$ ).

(a)

(b)

Figure 11: Experimentally extracted (a)  $I$ - $V$  and (b)  $P$ - $V$  characteristics of the PV modules under the *shading pattern B: PS* conditions. Values were measured at the PV side for both VMPV and string architectures.

### 3.1.4. Real-time maximum power point tracking

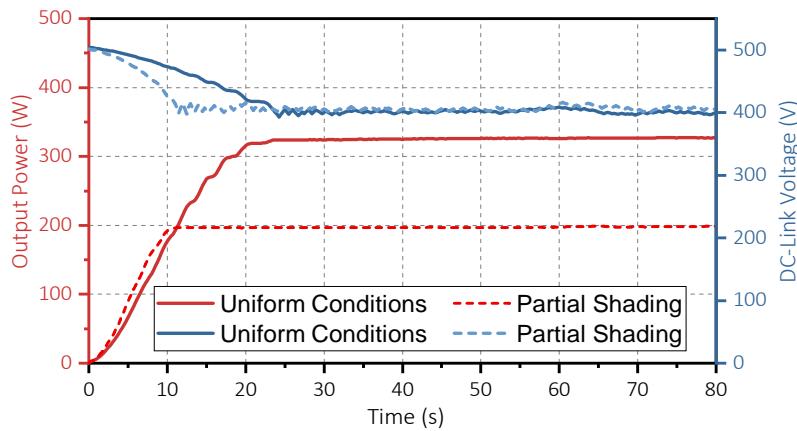

For this experiment, a P&O algorithm was executed by the second-stage converter, with a period of 250 ms and an MPPT duty cycle step of 1%. The two PV modules were subjected to the two shading patterns of the previous subsection (uniform and PS conditions). Figure 12 shows the output power and DC-bus voltage variation under real time tracking of the MPP. The MPPT algorithm always converges to the single MPP, guaranteeing near-perfect extraction efficiency at any conditions and effectively addressing the tracking challenges of SP configurations. In addition, the DC-link voltage is insignificantly affected by PS (only 3% deviation), which allows for a narrow predetermined input voltage range for the grid-side inverter, in contrast to the single-stage PV systems.

Figure 12: Response of the new VMPV architecture during real time MPPT, under uniform and PS conditions. Output power (in red) and DC-link voltage (in blue) variation with time.

### 3.1.4 Discussion and Future Work

Our goal was to demonstrate a highly efficient architecture for residential grid-connected PV systems to increase the energy yield from DEGs. Through the parallel connection at the output of a fixed-ratio high step-up  $nX$  converters we managed to eliminate the partial shading challenges of typical series connections and delivering almost 100% extraction efficiency. At the same time, the  $nX$  converter features a high flat conversion efficiency of more than 96.3% irrespective of the power level, leading to better total system efficiency at partial shading than most centralized and distributed PV architectures.

The use of GaN HEMTs in the developed magnetic-less  $nX$  converters allow for longer-lifetime ceramic capacitors in place of the conventional bulky electrolytic capacitors. This along with the omissions of all magnetic components and the low cooling requirements lead to a very compact solution that can be integrated to the backside of the PV panel, forming a new voltage-multiplied PV module.

All control functions, including MPPT, are transferred to the inverter, simplifying the DC-DC micro-converter requirements for microcontrollers and voltage/current sensors. The high-voltage parallel connection results in small variation of the DC-link voltage with the environmental conditions, which in turn simplifies the requirements for the grid-side inverter, as in two-stage string inverters.

Our proof of concept has been validated through simulations and experimental testing. However, the converter prototype is not yet optimized, in terms of power transfer capability and efficiency. In fact, the current version of the converter is oversized to handle 2.5 kW and occupies 0.1 liters of volume. The system can further be improved by using low-voltage rating HEMTs, with lower on-resistance and smaller footprint, that would improve the conversion efficiency and increase the power density. Additionally a soft-star-up circuit needs to be integrated to ensure reliable operation during power-up and shut-down.

Meeting these future goals will bring us one step closer to commercialization of the developed system. Our new approach offers a promising alternative to an already huge PV market.

### 3.2 Thermal management

As shown previously, the key enabling factor for high power density converters is the utilization of state-of-the-art GaN devices, which exhibit low specific on-resistance and high breakdown electric field [16], [17]. However, the increased switching frequencies and reduced die sizes cause high heat fluxes, surpassing  $1 \text{ kW/cm}^2$  [18], [19], which is far beyond the capabilities of conventional cooling methods [20]. Inadequate cooling of these devices causes high junction temperature which degrades their performance and reliability [21], [22].

The thermal challenges become more pronounced in converter topologies with a large number of active components, such as modular [23], [24] and composite topologies [25]. Uneven temperature rise over multiple devices causes hotspots that limit the system performance. Several modular air-based cooling topologies have been presented to cool down converters with a large number of components in a small form factor [26], [27], but the low heat transfer coefficient of air ultimately limits heat fluxes to roughly  $300 \text{ W/cm}^2$  [20]. To achieve higher power density in topologies with a large number of components, high-performance cooling techniques, such as liquid cooling, are required to surpass this limit.

Several high-efficiency liquid cooling strategies have been proposed for cooling of individual power devices, such as impinging coolant on the device [28], [29], as well as flowing coolant through microchannels [30]. The latter can result in state-of-the-art heat fluxes, due to its large surface area and high heat transfer coefficient [31]. However, microchannels typically suffer from high pressure drop. Approaches to reduce the pressure drop over microchannel heat sinks have received considerable attention [32]. A promising approach is the use of a manifold structure to distribute the flow over the microchannels [33]. This manifold microchannel (MMC) structure reduces the pressure drop, increases the temperature uniformity as well as a higher heat transfer [34], [35]. However, although these MMC heat sinks demonstrated in the literature have outstanding capabilities for high heat flux management [36]–[38], the complicated fabrication procedure, consisting of multiple bonding steps, has prevented large-scale adoption of this technology.

Consequently, there is currently no standard thermal management solution that can be mounted on a converter, like conventional heat sinks, while providing the high cooling performance of microchannels simultaneously to all active devices.

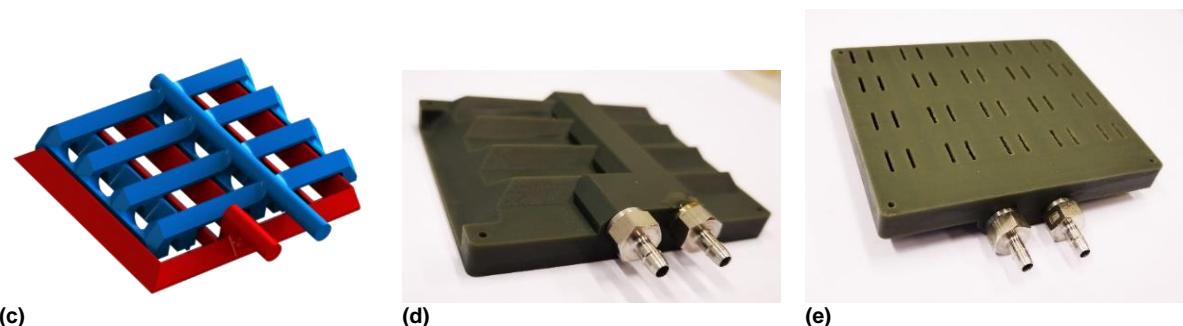

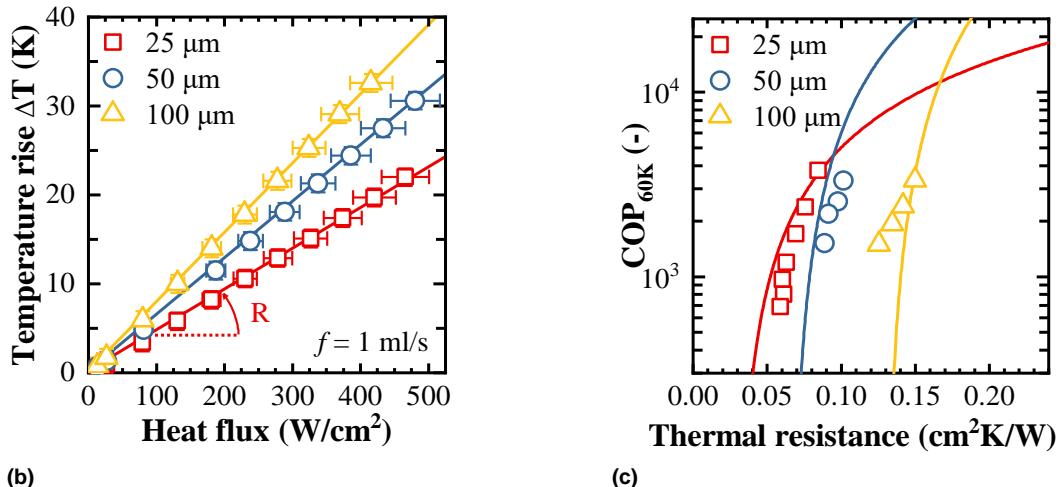

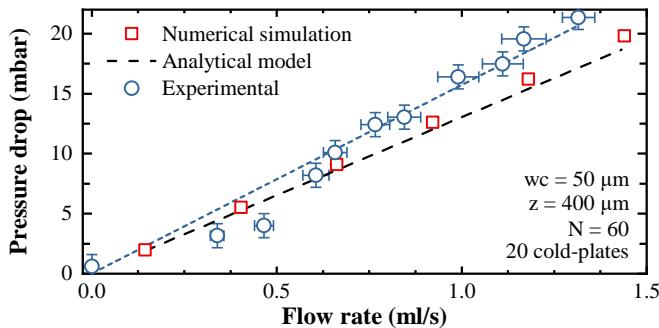

Within this project we propose a novel compact and energy-efficient microfluidic cooling system for power converters with multiple power devices by mounting microchannel cold-plates on each device. The high pressure drop usually associated with microchannels was minimized using a customized compact flow distribution manifold that connects these microfluidic heat-sinks in parallel to a common inlet and outlet. A model was developed to determine the optimal microchannel and manifold geometry that maximizes cooling capability and minimizes the required pumping power. Cold-plates were fabricated on silicon using standard clean-room processes, but could easily be replaced by high-throughput fabrication methods such as micro-deformation processes. We demonstrate flow distribution manifolds realized using 3D-printing as well as conventional fabrication methods to demonstrate the possibility of their mass-production in a cost-effective way. The thermal and hydraulic performance of the heat sink is experimentally evaluated and the cooling module, consisting of 20 silicon microchannel cold-plates, is demonstrated on the 2.5 kW switched capacitor converter, to demonstrate the potential of this new cooling system and its impact on power density. This proposed - method provides high performance microchannel cooling in a very compact form-factor with low pressure drop, making it a promising technology for future power converters.

#### 3.2.1 Modelling, Design and Fabrication

Here we derive the analytical expressions that describe the hydraulic and thermal performance of the heat sink, which are used to optimize the heat sink geometry for energy-efficient cooling. First, the cooling performance of an individual cold-plate is evaluated to obtain an optimum design, followed by the design and fabrication of the distribution manifold

### Micro-channel Cold Plates

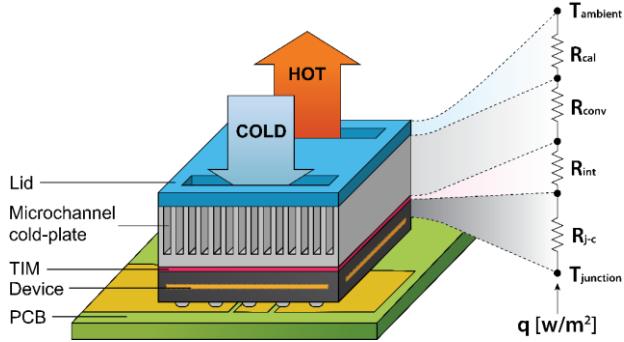

A schematic overview of the proposed cooling method is shown in Figure 13. A packaged device is mounted on a printed circuit board and cooled by a microchannel cold-plate attached on top of the device, separated by a thermal interface material (TIM). We investigate the situation where all dissipated power travels upwards to the microchannel cold-plate, which is the case if the device has a relatively low junction-to-case thermal resistance to the top of the device, and a high junction-to-board thermal resistance.

Figure 13: Schematic cross section of a transistor, cooled by a microchannel cold-plate, and an equivalent thermal resistance model.

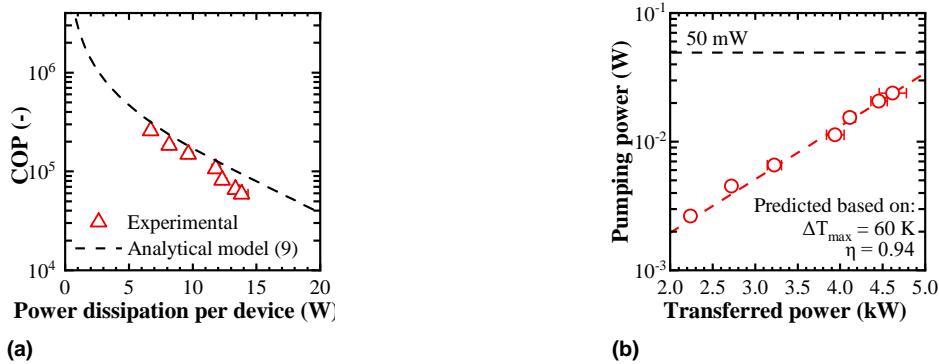

The cooling efficiency is described by the Coefficient of Performance (COP), given in (1), defined as the ratio of dissipated power in the system,  $Q_{max}$ , to the pumping power required,  $P$ , to keep the junction at a given maximum junction temperature,  $\Delta T_{max}$ . The pumping power, defined in (2), is the product of the flow rate,  $f$ , and the pressure drop  $\Delta p$ .  $R_{tot}$  is the total thermal resistance between the junction of the device and the inlet temperature of the coolant, which relates the heat losses to temperature rise according to (3). It is clear that to increase COP, the pressure drop, flow rate and thermal resistance have to be reduced. However, these values are interdependent, so to determine the optimal microchannel geometry, relations between pressure drop, thermal resistance and flow rate are required.

$$COP = \frac{Q_{max}}{P} \quad (1)$$

$$P = f \Delta p \quad (2)$$

$$\Delta T_{max} = Q_{max} R_{tot} \quad (3)$$

The total thermal resistance,  $R_{tot}$ , is the sum of the 4 components shown in the one-dimensional thermal resistance network in Figure 13.

- The *caloric thermal resistance* of the coolant,  $R_{cal}$ , given in (4), describes the temperature rise of the coolant between the inlet ( $T_{in}$ ) and the outlet ( $T_{out}$ ) and depends on the flow rate,  $f$ , the fluid density,  $\rho$ , and heat capacity,  $C_p$ .

- The *junction-to-case thermal resistance* of the device,  $R_{j-c}$ , is given by the device manufacturer and

- the *thermal interface resistance*,  $R_{int}$ , depends on the type of TIM used.

- the thermal resistance of the cold-plate is modeled as only a *convective thermal resistance*,  $R_{conv}$ , as expressed in (5), since the conduction component is negligibly small (<0.01 K/W) due to the high thermal conductivity of silicon.  $h$  is the heat transfer coefficient and  $A$  is the total surface area of the microchannels.

Using the fin model, previously described in [31], [39]–[41], an expression was derived for the convective thermal resistance, as shown in (5). The geometry of a microchannel is described by the channel width and fin width. We define  $w$  as both the channel and fin width, which simplifies the analytical expressions.  $z$  is the channel depth and  $Nu$  is the Nusselt number.  $\epsilon$  is the fin efficiency,

calculated using (6), where  $k_s$  is the thermal conductivity of the heat sink material and  $k_f$  the thermal conductivity of the fluid.

$$R_{cal} = \frac{T_{out} - T_{in}}{Q_{max}} = \frac{1}{\rho C_p f} \quad (4)$$

$$R_{conv} = \frac{1}{hA} \epsilon^{-1} = \left(1 + \frac{z}{w}\right)^{-1} \frac{w}{LWk_f Nu} \epsilon^{-1} \quad (5)$$

$$\epsilon = \tanh\left(z \sqrt{\frac{2h}{k_s w}}\right) \left(z \sqrt{\frac{2h}{k_s w}}\right)^{-1} \quad (6)$$

The required flow rate to keep the junction temperature rise at  $\Delta T_{max}$  can be calculated using (7). The relationship between pressure drop and flow rate in the microchannel cold plate can be expressed in terms of a hydraulic resistance,  $r_h$ . Considering a cold-plate with  $N$  parallel channels, the pressure drop can be calculated using (8) [42]. Combining equation (1)-(8) results in (9), an expression to calculate COP given a certain geometry and heat load. Eq. (9) shows that the coolant requires a high ratio of  $\rho^2 C_p^2 / \mu$ , which makes water a good candidate.

$$f = \left( \rho C_p \left( \frac{\Delta T_{max}}{Q_{max}} - R_{conv} - R_{int} - R_{j-c} \right) \right)^{-1} \quad (7)$$

$$\Delta p = r_h f = \frac{12\mu L}{N(1 - 0.63w/z)w^3 z} f \quad (8)$$

$$COP = \frac{\rho^2 C_p^2 Q_{max}}{r_h} \left( \frac{\Delta T_{max}}{Q_{max}} - R_{conv} - R_{int} - R_{j-c} \right)^2 \quad (9)$$

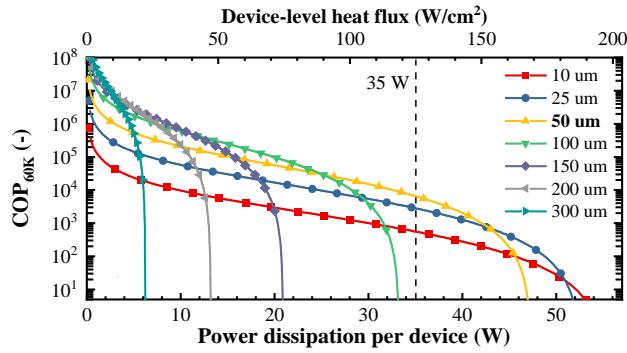

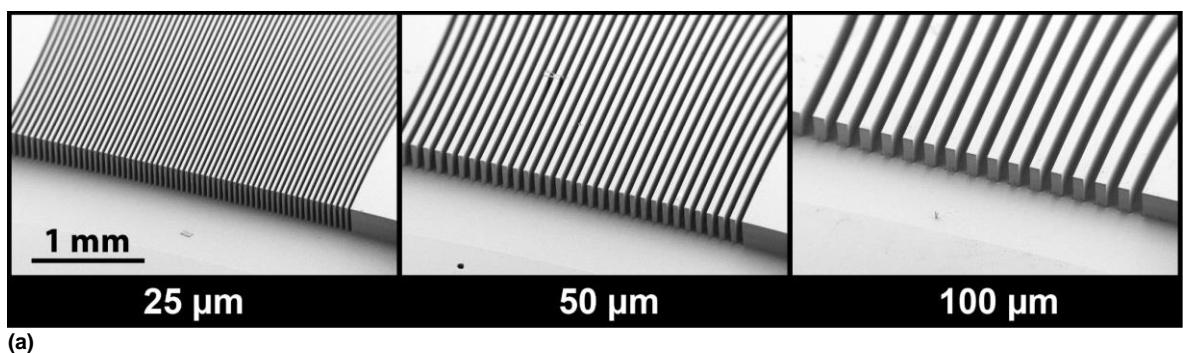

Using the aforementioned model, we studied the effect of channel size on the cooling performance of silicon microchannel cold-plates with channel depth  $z$  fixed at 400  $\mu\text{m}$  and channel width  $w$  varying between 10  $\mu\text{m}$  and  $w = 300 \mu\text{m}$ . Water was chosen as coolant and a typical value of 0.5 K/W was chosen for both  $R_{int}$  and  $R_{j-c}$  [43]. Figure 14 shows the calculated COP versus maximum dissipated power for microchannel cold plates. All curves show the same trend: COP decreases with increasing power due to the higher flow speed required to keep the temperature rise between the junction and the inlet temperature equal to  $\Delta T_{max} = 60^\circ\text{C}$ . After a certain power, a sharp cutoff in COP is observed due to the excessively high flow rates. Reducing the microchannel width results in an increase in  $Q_{max}$  at which this cutoff occurs, because of the reduced  $R_{conv}$ , however, at the cost of a lower COP at lower heat loads. For example, 25  $\mu\text{m}$  channels can extract approximately a 5-time higher heat load than 200  $\mu\text{m}$  channels but have a 10 times lower COP at low heat loads. For the nX converter described here,  $Q_{max}$  was estimated at 35 W, making 50  $\mu\text{m}$  channels the favorable design.

Figure 14: Calculated COP versus maximum power dissipation per transistor ( $Q_{max}$ ) cooled using the proposed microchannel cold-plate for channel widths varying between 10  $\mu\text{m}$  and 300  $\mu\text{m}$ , considering a maximum temperature rise  $\Delta T_{max}$  of 60  $^{\circ}\text{C}$ .

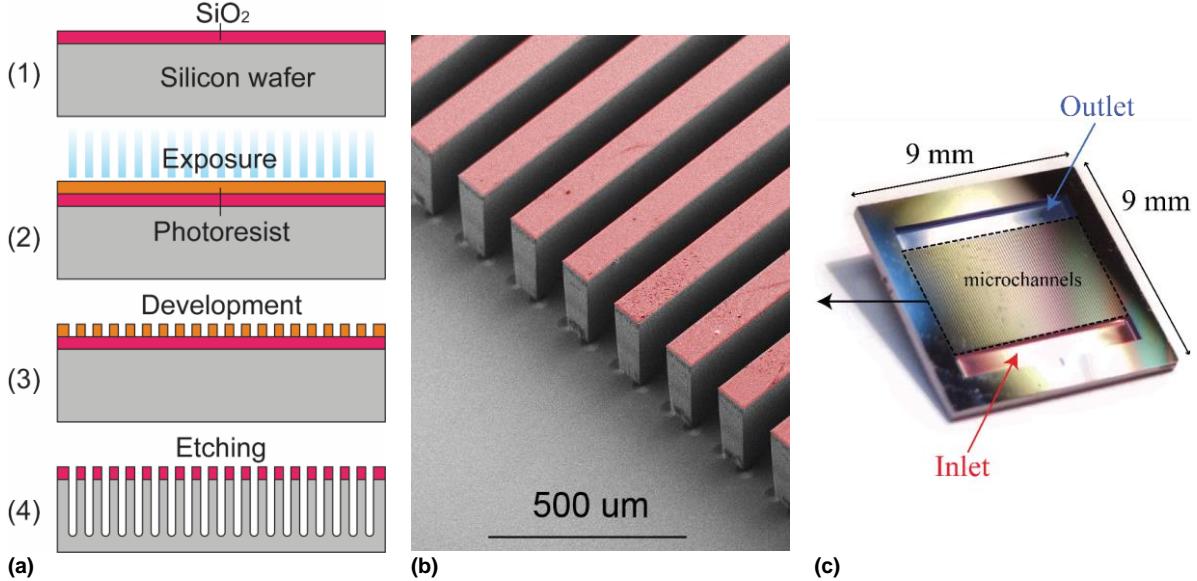

Microchannel cold-plates were fabricated on a 4-inch silicon wafer in the EPFL CMi cleanroom facilities, as illustrated in Figure 15(a). A 2  $\mu\text{m}$ -thick layer of  $\text{SiO}_2$  was deposited using plasma-enhanced chemical vapor deposition, which functions as a hard mask for dry-etching. Channels with widths between 25  $\mu\text{m}$  and 100  $\mu\text{m}$  were defined using photolithography followed by a dry-etch of the  $\text{SiO}_2$  using  $\text{C}_4\text{F}_8$  chemistry. Finally, 400  $\mu\text{m}$ -deep vertical channels were etched in silicon using the Bosch deep reactive-ion etching process. Inlet and outlet ducts were 1 mm by 7 mm rectangular openings. Figure 15 (b) shows a scanning electron microscope (SEM) image of the microchannels after etching. As a final step, the wafer was diced into individual 9 mm by 9 mm cold-plates, shown in Figure 15 (c).

Figure 15: (a) Fabrication process of the silicon microchannel cold-plates. (b) SEM image of the microchannels after etching, where false coloring indicates the presence of  $\text{SiO}_2$  (c) Picture of the cold-plate after dicing.

## Manifold

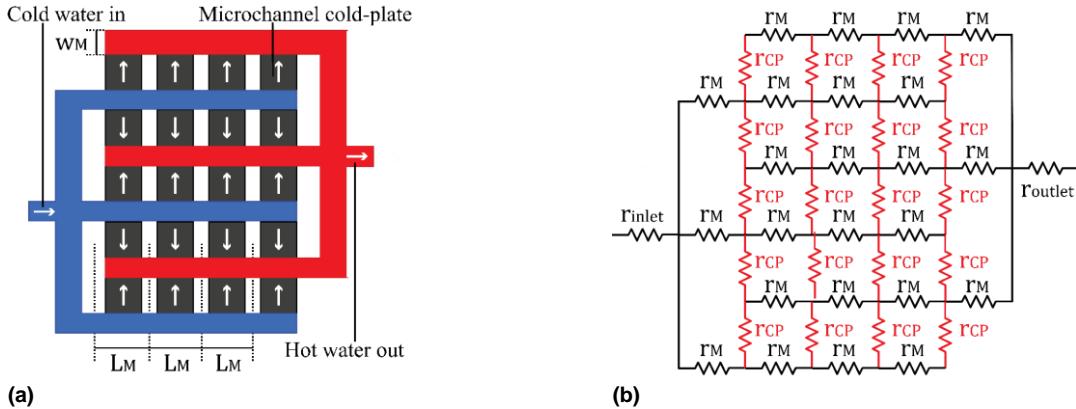

contact with the transistors on the PCB. Individual cold-plates can either be connected in series or in parallel. A series connection guarantees a consistent flow rate over all cold-plates, but suffers from a significantly higher pressure drop, as well as a higher temperature rise of the water at an identical flow rate. For this reason, it is favorable to parallelize the cold plates, as illustrated in Figure 16 (a). A careful manifold design is required to ensure an equal fluid distribution over all cold-plates and avoid local overheating [44], [45].

The cold-plate manifold was modeled as a network of resistors, illustrated in Figure 16 (b), where each resistor represents the hydraulic resistance of a specific part of the flow path. The hydraulic resistance of each cold-plate,  $r_{CP}$ , can be determined using (8), while the hydraulic resistance of the manifold inlet and outlet sections,  $r_M$ , calculated using (10). This equation gives the pressure drop of a square manifold channel section with cross-section  $w_M$  and length  $L_M$  [42]. The currents  $I_{CP,i}$  flowing through the resistors represent the flow rate in the cold-plates. Good flow uniformity can be guaranteed if  $r_{CP}$  is significantly larger than the sum of the hydraulic resistances over the manifold section. The percentage of variation of current from the mean,  $E_i$ , represents the flow non-uniformity, defined according to (11), which is used to assess the quality of the manifold design. A good design should have a low value of  $E_i$  such that the liquid is equally distributed over all cold-plates.

$$r_M = \frac{12\eta L_M}{0.42 w_M^4} \quad (10)$$

$$E_i = \left| \frac{20 \cdot I_{CP,i}}{\sum_{j=1}^{20} I_{CP,j}} \right| - 1 \quad (11)$$

Figure 16: (a) Illustration of the liquid flow through the manifold. (b) An equivalent hydraulic resistance network of the manifold and the microchannel cold plates.

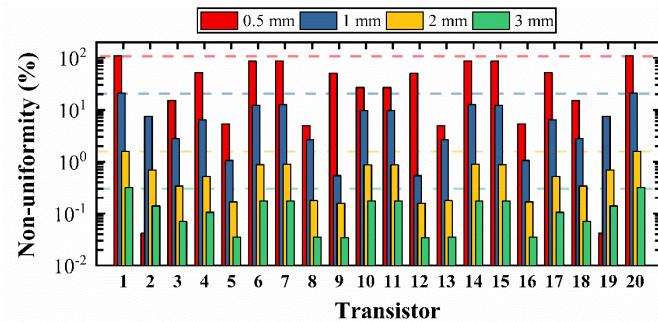

We investigated the flow uniformity of a manifold delivering coolant to a  $4 \times 5$  grid of transistors, using microchannel cold-plates with the following characteristics:  $N = 80$ ,  $w = 50 \mu\text{m}$  and  $z = 300 \mu\text{m}$ ,  $L = 6 \text{ mm}$ . The manifold had equal section length  $L_M$  of 2 cm and their cross-section  $w_M$  was varied from 0.5 mm to 3 mm to study its impact on the flow uniformity. *LTspice* was used to calculate the currents in the resistor network, which corresponds to the flow distribution through all 20 cold-plates. Figure 17 shows the percentage of flow non-uniformity, which strongly depends on the manifold channel size. For  $w_M = 0.5 \text{ mm}$ , the flow rate non-uniformity is above 100%, whereas for  $w_M = 2 \text{ mm}$  the non-uniformity is limited to approximately 1%. This result clearly shows the importance of properly sizing the manifold for obtaining a uniform distribution of coolants to the cold plates.

Figure 17: Flow rate non-uniformity for manifold cross-section width  $w_M$  varying from 0.5 mm to 3 mm, defined as the percentage of absolute deviation of flow rate from the mean for all 20 cold-plates.

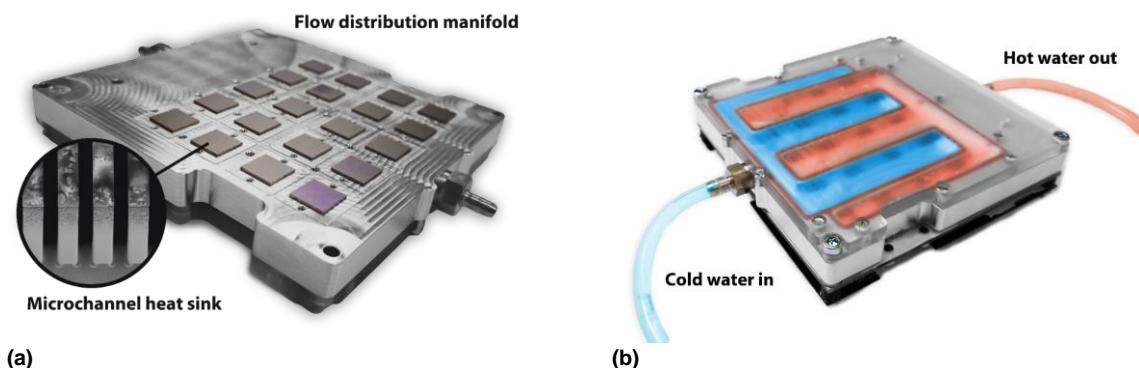

Two flow distribution manifolds were fabricated based on the design rules from the previous simulation. The first manifold, shown in Figure 18 (a), was realized using Computer Numerical Controlled (CNC) machining and consists of three pieces: an aluminum body, a polycarbonate lid and a silicone gasket to provide leak-tight seal. This simple design can be easily fabricated by injection molding for low-cost mass manufacturing. The bottom side of the manifold contains 40 slits connected to the inlet and outlet of 20 silicon microchannel cold plates. The cold-plates were connected to the manifold using a water-resistant double-sided adhesive, which was laser-cut to size. Figure 18 (b) shows the top side of the manifold where the red and blue colors indicate the hot and cold water, respectively.

A more compact manifold was fabricated using stereolithography (SLA) 3D printing. The possibility to 3D print the manifold is very interesting for rapid prototyping together with the electronic design. This way, the geometry of the cold-plate defines the cooling performance whereas the manifold defines the distribution of the coolant. Additionally, by removing the constraints of conventional fabrication methods, more compact designs can be realized. A network of overlapping inlet and outlet channels was designed, shown in the computer-aided design (CAD) model of Figure 18 (c), where the blue and red colored sections indicate the hot and cold water, respectively. Such a design cannot be realized using conventional CNC machining, but additive manufacturing enables the realization of such a monolithic structure. High temperature resist was used (EnvisionTEC HTM140) which can withstand temperatures up to 140 °C. The sidewalls of all channels were angled at 45 degrees to print the structure without internal support material, as this would be impossible to remove from the monolithic structure. Figure 18 (e) and (e) show the manifold after printing. The slits visible in Figure 18 (c) connect to the inlet and outlet of the silicon microchannel cold-plates. The total volume of this manifold is only 35 cm<sup>3</sup>.

Figure 18: (a) Bottom side of the Aluminum CNC-machined manifold with 20 silicon microchannel cold plates and (b) top side with a polycarbonate lid. (c) CAD model of the 3D-printed manifold (d) Top side of the manifold after 3D printing. (e) Bottom of the manifold which shows the slits that connect the manifold to the microchannel cold-plates.

### 3.2.2 Experimental Evaluation

#### Micro-channel Cold Plates

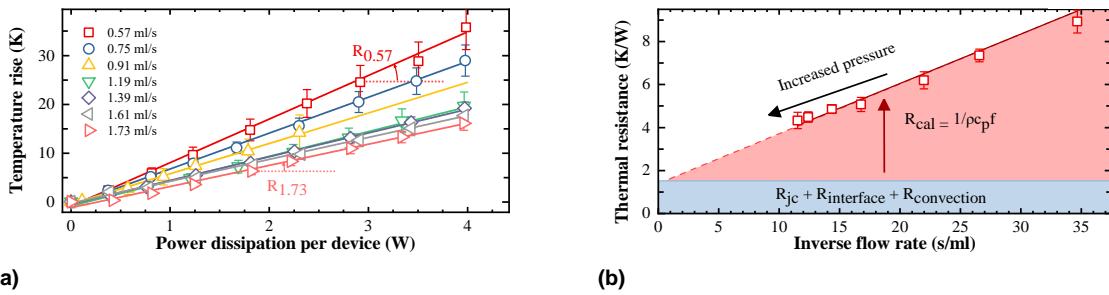

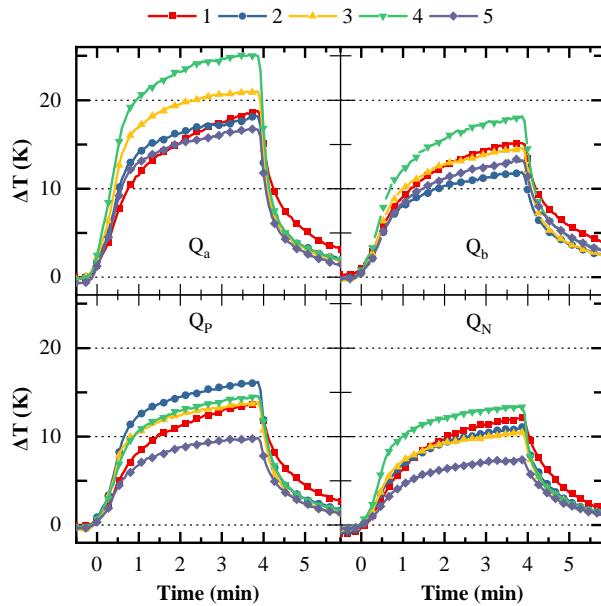

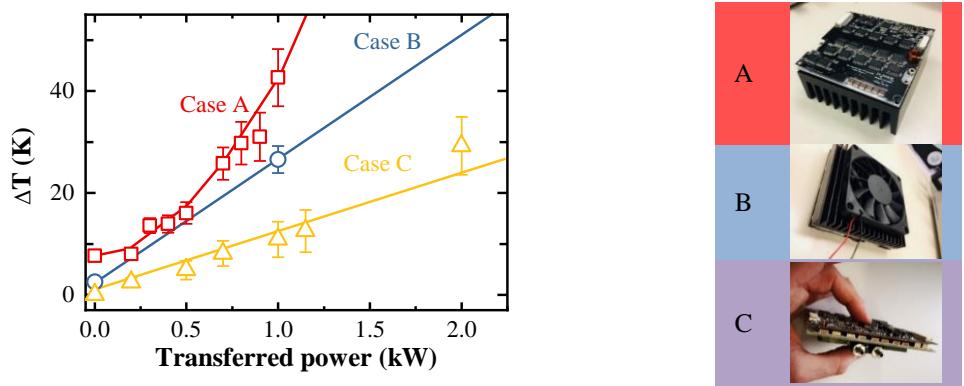

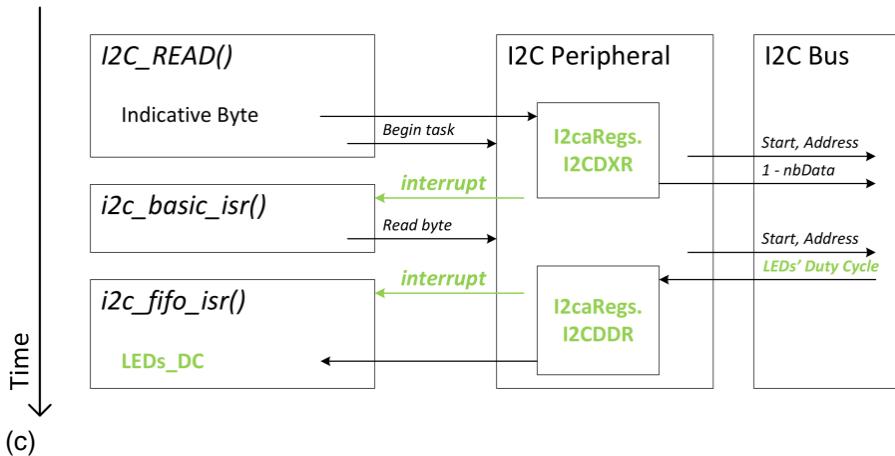

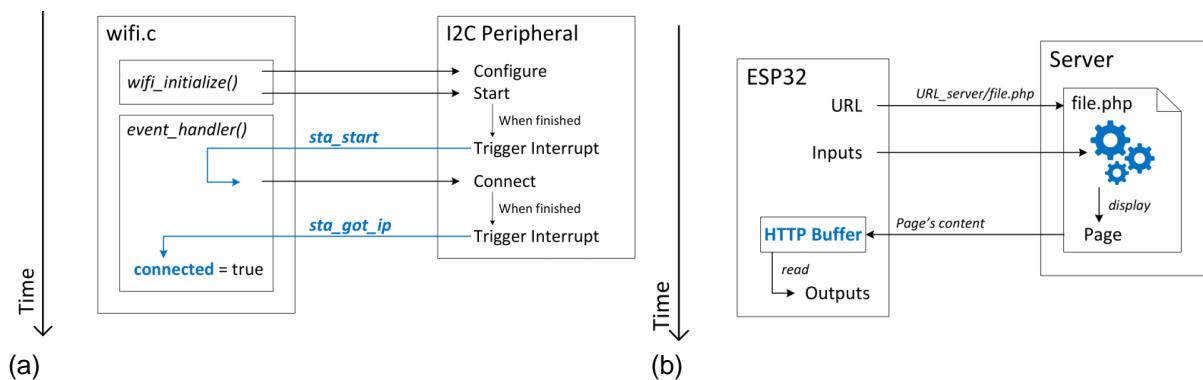

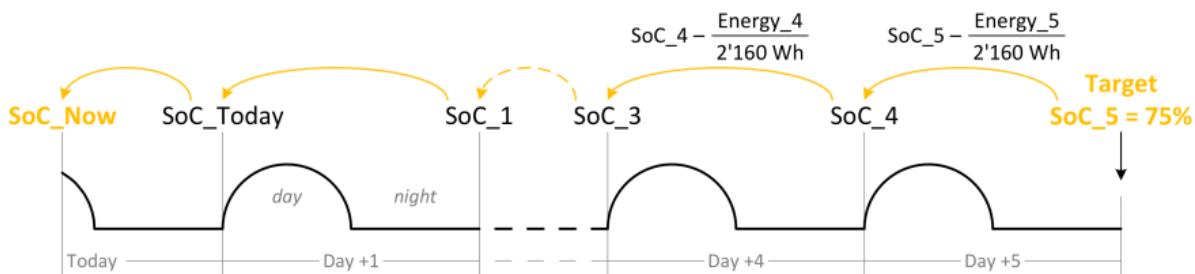

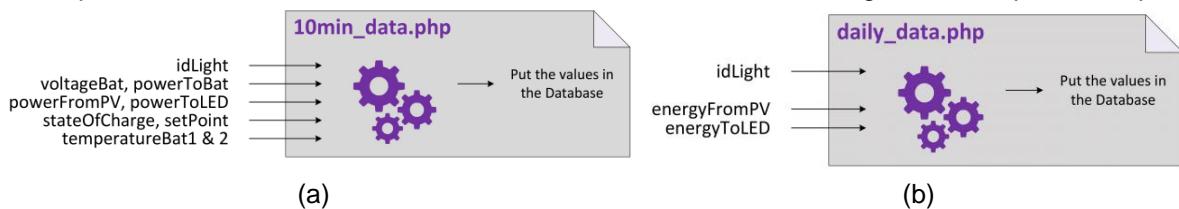

A test setup was developed to experimentally investigate the performance of microchannel cold-plates of various channel dimensions. This setup, illustrated in Figure 19 (a), contains a pressure regulator that pressurizes a reservoir with deionized (DI) water. The DI water flows, through a flow meter into the test section that contains an individual microchannel cold-plate. This test setup includes 2 calibrated thermocouples that measure the water temperature before and after the cold-plate and a pressure sensor to determine the pressure drop over the cold-plate.