Swiss Federal Office of Energy SFOE Energy Research

**Annual report 2016**

# **Swiss Inno-HJT**

Pilot production and demonstration of innovative high performance silicon hetero-junction PV cells, modules & systems

© XY 2016

Date: 09.12.2016

Town: Hauterive (NE)

#### **Publisher:**

Swiss Federal Office of Energy SFOE P+D Programme CH-3003 Bern www.bfe.admin.ch

#### Co-financed by:

Etat de Neuchâtel - Service de l'économie Avenue de la Gare 2, CH-2000 Neuchâtel

#### Agent:

Meyer Burger Technology AG Schorenstrasse 39, CH-3645 Gwatt www.meyerburger.com

#### **CSEM SA**

Rue Jaquet-Droz 1, CH-2000 Neuchâtel www.csem.ch

Meyer Burger Research AG Rouges-Terres 61, CH-2068 Hauterive www.meyerburger.com

Pasan SA Rue Jaquet-Droz 8, CH-2000 Neuchâtel www.pasan.ch

#### Authors:

Benjamin Strahm, Meyer Burger Research AG, <u>benjamin.strahm@meyerburger.com</u> Matthieu Despeisse, CSEM SA, <u>matthieu.despeisse@csem.ch</u>

SFOE head of domain: Stefan Nowak, Stefan.nowak@netenergy.ch

SFOE programme manager: Stefan Oberholzer, stefan.oberholzer@bfe.admin.ch

SFOE contract number: SI/500966-01

The author of this report bears the entire responsibility for the content and for the conclusions drawn therefrom.

### **Swiss Federal Office of Energy SFOE**

Mühlestrasse 4, CH-3063 Ittigen; postal address: CH-3003 Bern Phone +41 58 462 56 11 · Fax +41 58 463 25 00 · contact@bfe.admin.ch · www.bfe.admin.ch

#### **ABSTRACT**

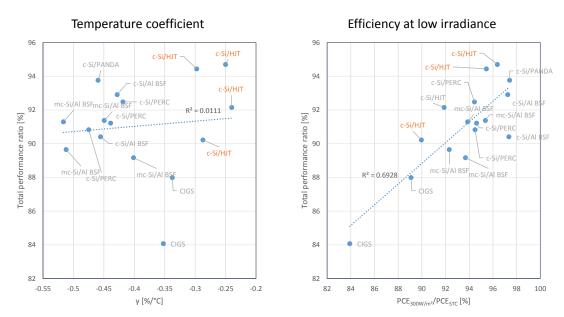

The Photovoltaics market has been driven in the last decade by strong increase of module production per year, with > 50 GW in 2015 and predictions for 100 GW after 2020. State-of-the-art products demonstrate efficiencies of 17–18 % and 19–20 % respectively, while increasing market share of high performance silicon technologies are expected, targeting the competitive production of > 22.5 % cells. In that respect, the Silicon Heterojunction Technology (HJT) developed and matured in Switzerland by Meyer Burger is of key relevance, owing to its high conversion efficiency achieved with limited number of production steps (a pre-requisite for keeping reduced costs). In this context, the Swiss-Inno HJT project focused on the demonstration at the pilot scale of cost-competitive manufacturability of high performance silicon solar cells, modules and systems, based on the key processes and technologies expertise of the Meyer Burger group and of CSEM, with the objective to transfer this high power output technology with low production costs to the photovoltaic market.

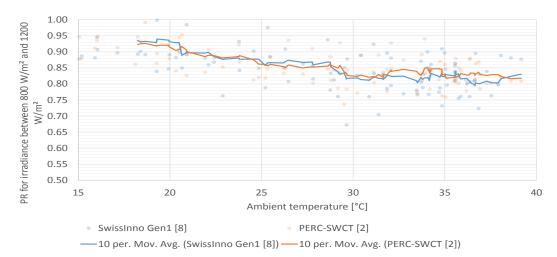

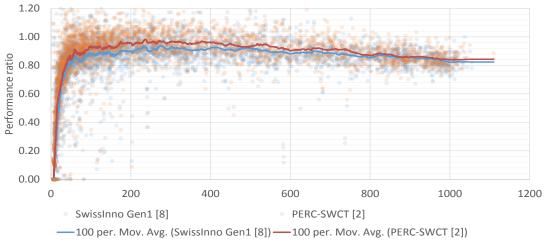

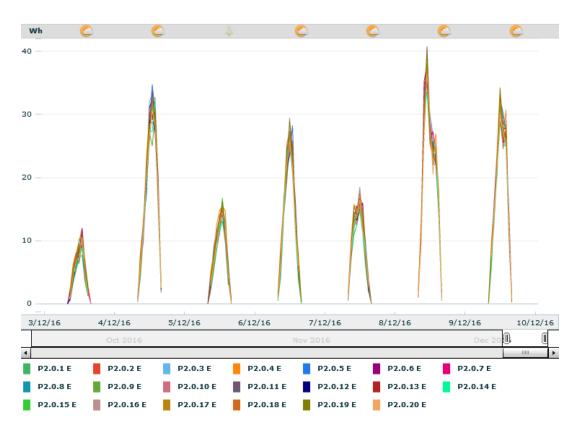

Pilot lines were installed and ramped-up for HJT cells manufacturing, with innovations conducted at material, processes and design levels. The project enabled going from 21 % cell efficiency using labtools to 22.2 % average efficiency achieved with Meyer Burger mass-production equipment, and with efficiencies up to 22.8 % achieved with CSEM metallization R&D pilot line. This was achieved on bifacial cells and with > 30 % cell manufacturing costs reduction (only 0.4 CHF/wafer for the last cell generation). These achievements in a mass-production relevant environment demonstrate the feasibility of manufacturing high efficiency HJT cells at extremely competitive costs. The innovative SmartWire module technology was demonstrated to enable for high performance, with 330 Wp record module. Two generations of modules were manufactured in 2016 using bifacial heterojunction cells produced in the pilot lines, showing performance in the 300 Wp range, with potential for enhancement to 310-320 Wp class based on the achieved cell efficiency and module developments. The third module generation demonstrated materials cost reduction enabling to achieve down to 40 CHF/module. The cumulated wafers, cells and modules costs using technologies demonstrated in this project result in a minimum calculated cost of 0.41 CHF/Wp for the demonstrated silicon heterojunction technology, achieving strong reduction in comparison to the initial project targets, enabling for high competitivity. Finally, two-monitoring sites were completed in the project, with the 3 generations of produced modules installed on the publicly visible site next to the port and Latenium site in Hauterive, NE. The modules were successfully installed and performance monitoring initiated. First data collected indicate performance ratio potential for the developed technology in par with the project targets of > 91 %. The data analysis typically requires averaging of 1-year data for reliable performance analysis, and will be finalized therefore for the second and third generations of modules in the course of 2017.

The project achievements provided high visibility of the outstanding results achieved in Switzerland on these technology developments. The pilot lines enabled for acceleration of the developments for competitive HJT cells manufacturing, and for demonstration to potential clients. First industrial projects for silicon heterojunction cells manufacturing could be concluded by Meyer Burger in Europe, Russia and Asia. The Meyer Burger Silicon HJT technology is today further placed on the roadmap of most of the cells manufacturers worldwide. The remaining hurdles for wider integration are today linked to the initial CAPEX expenditure to be realized. Further developments in that direction will be key to achieve full industrial success.

## **Project goals**

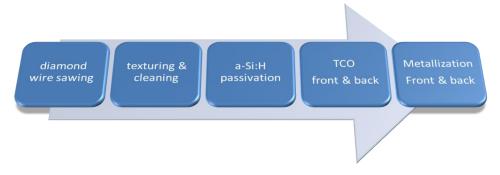

The goal of the *Swiss Inno-HJT* project was to demonstrate the superior performance of photovoltaic systems based on silicon heterojunction solar cells and modules manufactured on mass-production equipment at competitive costs. This fully integrated R&D project dealt with all processing steps including the monocrystalline wafer sawing using diamond wire technology, high efficiency silicon heterojunction solar cell processing, advanced cell metallization, advanced module integration using Smart Wire Technology and finally outdoor testing and demonstration. Key to the project goals, all these steps were made on pilot lines with mass production relevant processes and tools to demonstrate the commercial viability of the demonstrated technologies. This directly supports the world-wide dissemination of the silicon heterojunction technology using Swiss made equipment and technologies.

At the project initiation, efficiency up to 21 % could be demonstrated on 6 inches-commercial wafers in the premises of Meyer Burger Research, on R&D fabrication equipment. The first key goal of the project was related to the installation of a "core process" pilot line for the manufacturing of silicon heterojunction solar cells, using mass-production PECVD and PVD equipment and to the demonstration at this pre-industrial production stage of solar cells with up to 22.5 % efficiency. The second key objective of the project was linked to the development and demonstration of alternative metallization and interconnection technologies enabling to drastically reduce the costs related to the cell metallization, while guaranteeing the achievement of > 22.5 % conversion efficiency. More particularly, the development of plating technology for bifacial cells, manufactured in a R&D pilot line, was targeted at CSEM in that respect. The third key objective was then set to manufacture different cells and modules generations (from Gen1 to Gen3), and enabling to achieve up to 21 % module efficiency, keeping production costs below 0.65 CHF/Wp. The fourth key goal was finally the installation and monitoring for each module generation of 3 kW<sub>p</sub> capacity, to demonstrate > 91 % performance ratio with the developed technologies. Overall the Swiss Inno HJT therefore targeted the acceleration of the pilot development of the silicon heterojunction cells and modules technologies, with focus on pre-industrial manufacturing, cell efficiency increase, cost reduction achievement, and on module monitoring for the demonstration of the high performance of the developed technologies.

## **Summary**

During the Swiss Inno-HJT project, a fully integrated research and development structure has been set-up at CSEM and Meyer Burger. This pilot production has been used to demonstrate the economical relevance of silicon heterojunction solar cells and modules manufactured with Swiss technologies. Along the project duration, developments have led to 3 different generations of HJT solar cell and modules starting from the traditional monofacial structure, up to a high performance bifacial structure. The solar cell efficiency has been increased from 21.5% at the start-up of the pilot line up to 22.8% at the end of the project and thus with a switch from monofacial to bifacial design. This achievement was accompanied with a cell manufacturing cost reduction of more than 30 %.

A total of 39 modules have been manufactured during the project and have been installed for outdoor monitoring. The manufacturing cost of these modules has been reduced drastically by the use of new materials and innovative technologies. The first module generation made in 2015 were manufactured at an estimated cost of 0.64 CHF/Wp, reaching already the project target. In 2016, it has been demonstrated that the manufacturing cost per module can be decreased by about 40% while keeping the high power output of 300 W per module, hence reaching 0.4 CHF/Wp. This achievement done in a mass production relevant environment demonstrates the feasibility of silicon heterojunction manufacturing at extremely competitive costs. Moreover, we can forecast a further drop in cost down

to 0.3 CHF/Wp by 2020 by the introduction of thin wafers and cheaper manufacturing technologies and processes.

## Work undertaken and findings obtained

2016 focus was on the production of cells and modules with technologies and processes developed during 2015 on the HJT cell and module pilot lines.

In the first section of this chapter, the Gen 2 cells and modules produced in spring 2016 and the Gen 3 cells and modules produced in fall 2016 are presented. Detailed manufacturing cost analysis is as well presented.

In a second section, more details about the development of the technologies and processes incorporated in Gen 2 and Gen 3 cells and modules are given.

## 1. Cell and module production

### 1.1 Cell production

#### 1.1.1 Gen 2 silicon heterojunction cell production

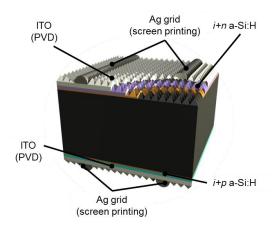

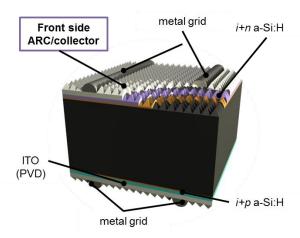

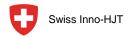

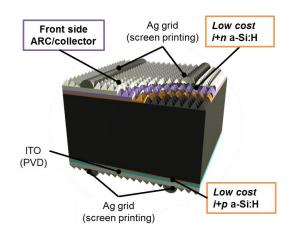

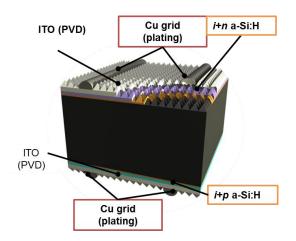

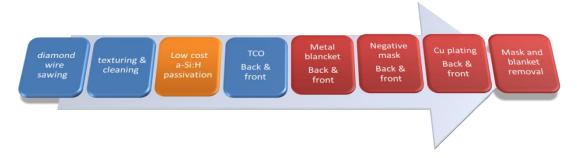

Gen 2 cells were planned to be monofacial, but increased market interest into bifacial devices pushed us to modify the original plan. Therefore, instead of waiting until Gen 3 cells and modules to introduce bifacial structure, it has been decided to accelerate the development and work on the back side of Gen 1 HJT solar cells to make them bifacial by the substitution of the full metal blanket by a screen printed metal grid as shown in the process flow in Figure 1.1. As shown in Figure 1.2, the resulting cell structure is symmetric with ITO and screen printed metal grid on both sides of the solar cell.

Because of this modification of cell structure from monofacial to bifacial, the efficiency target for Gen 2 cells, i.e. 22.5% <sup>GT</sup>, is not relevant anymore. Therefore, the target of Gen 3 bifacial cells, i.e. 21.5% <sup>GT</sup>, has to be used as the new target for Gen 2 cells as well.

Figure 1.1: process flow of Si-HJT Gen 2 cells

The produced cells have the following specifications:

- n type CZ wafers 156x156 mm, 200 mm diameter (239 cm<sup>2</sup>)

- cut by diamond wire ~150 μm thick

- rear side emitter (p layer on back side)

- bifacial design with ITO on both sides.

- busbar less screen printed front and back grid.

measured with Grid<sup>TOUCH</sup> contacting unit with a black non-reflective background.

The most important features of these cells compared to the Gen 1 cells are:

- 1. The wafer thickness has been reduced considerably from as cut thickness of 180  $\mu m$  to 150  $\mu m$  to reduce wafer costs and evaluate the impact of thinner wafer on bifacial device performance. This has been made possible thanks to work conducted in 2015 on the sawing development that has been described in the 2015 report of the *Swiss Inno-HJT* project.

- 2. The rear side Ag/NiV full area metallization deposited by PVD of the Gen 1 cells has been replaced by a screen printed silver grid. The rear side grid design used for the production has been selected out of the development work carried out by CSEM (see section on conducted developments). In addition, the rear side ITO layer has been adapted to optimize cost without major impact on performance. This optimization has been performed on the R&D pilot sputtering tool at Meyer Burger Research.

Figure 1.2: HJT solar cell structure used for Gen 2 cells.

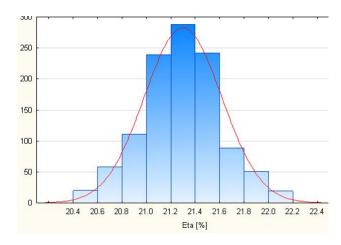

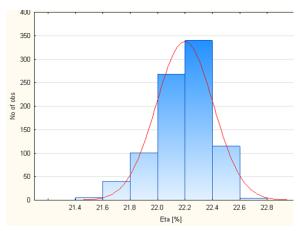

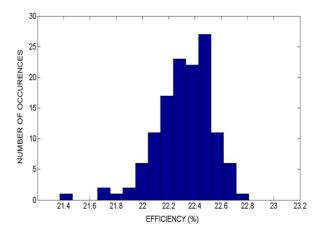

**Figure 1.3**: efficiency distribution of >1'100 Gen2 cells as measured with the Grid<sup>TOUCH</sup> contacting unit..

Figure 1.3 shows the efficiency distribution of the 1'117 Gen 2 bifacial cells produced in spring 2016. It exhibits a nice Gaussian distribution with a median efficiency of 21.3  $^{\rm GT}$  and best cell at 22.1  $^{\rm GT}$ . Cell parameters are summarized in Table 1.1 together with Gen 1 median values for comparison. Gen2 revised target efficiency of 21.5 $^{\rm GT}$  has not been reached for this first generation of bifacial devices. However, best measured efficiency are far above the target showing the potential of this structure. Analyzing the Table 1.1 more in details, we can conclude that the achieved mean efficiency suffers from passivation issues. Indeed, the  $V_{oc}$  even if at the same level as Gen 1 cells was expected to be higher because of the thinner wafer used for Gen 2 cells. Moreover, the FF is as well showing some weaknesses compared to Gen 1, suggesting as well some passivation limitation. However, high values for both  $V_{oc}$  (739 mV) and FF (80.3%) have been reached on the champion Gen 2 cell showing that there is no physical limitation behind the limited median values. This will be the focus for the Gen 3 cells presented later in this report.

On the other hand, the short circuit current values are very close between Gen 1 (37.6 mA/cm $^2$ ) and Gen 2 (37.4 mA/cm $^2$ ) cells. This is a very impressive achievement given the fact that the Gen 2 cells have two major drawbacks compared to Gen 1 in terms of photocurrent generation: they are bifacial and made with thinner wafers. Therefore, they are more transparent to infrared light than Gen 1 cells. This achievement has been made possible by the development done on the back side ITO properties but also thanks to the reduction in plasmonic absorption at the ITO/Ag interface of Gen 1 cells. Indeed, Gen1 cells have been optimized in terms of \$W\_p\$ and the back side reflector performance was not the best in class.

Table 1.1: Gen2 cell median and best IV parameters, measured using the PASAN Grid TOUCH technology.

|              | eff<br>(% <sup>GT</sup> ) | Voc<br>(mV) | FF<br>(%) | Jsc<br>(mA/cm²) |

|--------------|---------------------------|-------------|-----------|-----------------|

| best         | 22.14                     | 739         | 80.27     | 37.34           |

| median       | 21.29                     | 728         | 78.1      | 37.41           |

| Gen 1 median | 21.5                      | 725         | 78.9      | 37.6            |

Despite the lower efficiency of Gen 2 cells than the 21.5% target, we have seen that the bifaciality of a device does not mean that high efficiency cannot be reached. Of course, the best bifacial device will always suffer from lower photo-generated current than well optimized monofacial device, but it has been shown that there is no physical limitations prohibiting bifacial devices with efficiencies above 22.5% of not even higher.

#### 1.1.2 Gen 3 silicon heterojunction cell production

Gen 3 cells have been produced during the second half of 2016 and consist, as for Gen 2 cells, in bifacial devices. Cells have been produced in 3 groups introducing in each group a new technology or process evolution, if not revolution. Focus for Gen 3 cells, as well as module as it will be shown later, has been made on cost reduction. Indeed, the market prices of PV cells and modules have dropped significantly during 2016 and the *Swiss Inno-HJ*T cost target of 0.65 CHF/Wp is today not sufficient to have a competitive technology with todays' market prices of about 0.4 CHF/Wp.

All groups have been manufactured with similar base specifications:

- *n* type CZ wafers 156x156 mm, 200 mm diameter (239 cm<sup>2</sup>)

- cut by diamond wire ~180 μm thick

- rear side emitter (p layer on back side)

- bifacial design

- · busbar less design.

- measured with Grid<sup>TOUCH</sup> contacting unit with a black non-reflective background.

Compared to Gen 2 cells, only the wafer thickness has been changed to favor high efficiency bifacial devices. The 3 groups are described briefly in the Table 1.2. Each of them addresses a specific cost driver:

- Group 1 introduces a new front side transparent conductive oxide and antireflective concept with a new material bill for lower light parasitic losses and costs. All other processes are identical to Gen 2 cells. This new structure is named Si-HJT 2.0.

- Group 2 introduces new PECVD processes that reduce significantly the amorphous silicon deposition costs. This is done in combination with the Si-HJT 2.0 cell structure.

- Group 3 uses copper plated metallization grids at the front and back side of the solar cells.

Plating is achieved in the plating pilot line at CSEM as described in the development section of this report. This group combines plating and low cost PECVD processes, but not the Si-HJT 2.0 cell structure.

**Table 1.2**: the 3 different groups of Gen 3 cells.

|                   | Group 1<br>(873 cells)                     | Group 2<br>(187 cells)                     | Group 3<br>(130 cells) |

|-------------------|--------------------------------------------|--------------------------------------------|------------------------|

| Front side<br>TCO | New low cost<br>materials and<br>structure | New low cost<br>materials and<br>structure | Standard               |

| PECVD             | standard                                   | New low cost processes                     | New low cost processes |

| Metallization     | Ag screen printing                         | Ag screen printing                         | Cu plating             |

#### Group 1: Si-HJT 2.0 cell structure

The first group of the Gen 3 cells tackles the high front side ITO cost and photon losses. Indeed, the front side ITO is one of the drawback of Si-HJT cells because of its cost since it is made from Indium and as well because of light absorption losses because of its high carrier density. Several approaches have been proposed in the recent years but all of these new technologies improve one or the other of these drawbacks but in general never both at the same time. We can even say that when one is improved the other one is degraded. This can be described into 2 examples:

- Front side ITO can be replaced by Indium oxide doped with various element such as hydrogen, tungsten oxide or cerium oxide. By doing so, the carrier density can be significantly reduced increasing then the photo-generated current. The electrical properties of the TCO is kept constant by an improvement of the carrier mobility usually observed in such king of TCOs. However, TCOs still contains Indium and therefor are not cheaper. Moreover, these materials are very brittle compared to ITO and more complicated to manufacture. Therefore manufacturing costs increase and the deposition technique have to be adapted to the new materials generating additional costs since these techniques are generally more complicated than magnetron sputtering.

- Another option is to substitute ITO by low cost TCOs, such as Zinc Oxide doped with element such as aluminium. Definitively the cost can be reduced considerably by this way since Zinc oxide sputtering targets are about 3 times less expensive than ITO targets and both materials can be deposited by the same low cost sputtering equipment. However, Zinc oxide based TCO have not the same electrical and optical performance than ITO and the cell efficiency drops at least by 0.5% absolute.

The Si-HJT 2.0 cell structure (Figure 1.4) solves both of these drawbacks of ITO at the same time by only separating the TCO processes for front and back side with the only disadvantage to add one processing step as sketched in Figure 1.5. Since the IP protection of this new process and cell structure is still ongoing, no further details about this technology can be shared in the present report.

Figure 1.4: Si-HJT 2.0 solar cell structure used for Gen 3.1 cells.

However, what can be disclosed is the effect of such structure on the cell performance as well as the cost reduction. As shown in Figure 1.6, the efficiency of such device surpasses the classical Si-HJT structure and thus mostly by an increase in short circuit current. Indeed, in this example the short circuit current density increases by more than 1 mA/cm $^2$ . Not all of this increase can be attributed to the Si-HJT 2.0 structure, but based on other experimental results we can state that 0. 4 to 0.5 mA/cm $^2$  can be attributed to the change of material bill at the front side. The remaining gain comes from the increased wafer thickness as well as to optimized metallization to reach a trade-off between  $J_{sc}$  and FF.

Figure 1.5: process flow of Si-HJT 2.0 Gen 3 cells

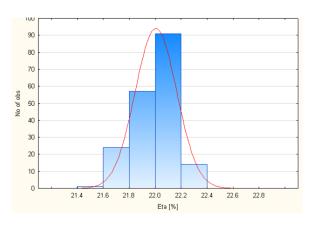

Concerning the passivation quality, we can see that the  $V_{oc}$  is increased when compared to Gen 1 and Gen 2 cells despite the thicker wafers used in the case of Gen 3 cells. This demonstrates that the passivation quality issues pointed for Gen 2 (and Gen 1) cells have been solved, at least partially. This is confirmed by the lower spread in data as shown in Figure 1.7 where the distribution is no longer a Gaussian. Moreover, the difference between best device and median cell parameters is significantly reduced as shown in Table 1.3 compared to Gen 2 cells, demonstrating once more the improved quality and uniformity of the cell process in the pilot line.

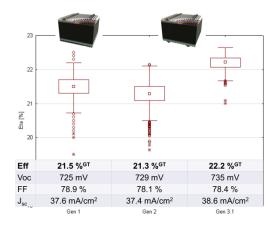

**Figure 1.6**: Si-HJT 2.0 cell performance compared to monofacial Gen 1 and bifacial Gen 2 cells.

Figure 1.7: efficiency distribution of >850 Gen3.1 cells as measured with the Grid<sup>TOUCH</sup> contacting unit..

Table 1.3: Gen3.1 cell median and best IV parameters, measured using the PASAN Grid TOUCH technology.

|        | eff<br>(% <sup>GT</sup> ) | V <sub>oc</sub><br>(mV) | FF<br>(%) | J <sub>sc</sub><br>(mA/cm²) |

|--------|---------------------------|-------------------------|-----------|-----------------------------|

| best   | 22.65                     | 737                     | 79.3      | 38.76                       |

| median | 22.2                      | 734                     | 78.4      | 38.56                       |

The median cell efficiency is 22.2 %<sup>GT</sup> and exceeds the target for bifacial device by 0.7%<sup>GT</sup> absolute. The best device breaks the 22.5% mark with a recorded 22.65%<sup>GT</sup> efficiency, mostly thanks to a high FF than the median cell efficiency. This achievement paves the way towards mean efficiencies higher than 22.5% with bifacial devices manufactured in production conditions.

#### Group 2: Si-HJT 2.0 with low cost a-Si processes

The group 2 of Gen 3 cells is similar to the group 1 in term of solar cell structure, but in addition to the Si-HJT 2.0 front side light management structure comprises new processes for the amorphous silicon layers as shown in Figure 1.8. The goal of these new layers is to reduce the manufacturing costs without impacting the conversion efficiency. Indeed, up to now the silicon layers have been developed to deliver the highest passivation quality without any compromise. These new layers are the results of questioning about what is mandatory or not to provide this excellence in surface passivation. The final process flow is not changed compared to the Si-HJT 2.0 structure as shown in Figure 1.9 and modifications compared to previous processes are mostly in recipes and hardware configuration. For obvious reasons, these modifications cannot be disclosed in the present document.

Figure 1.8: HJT solar cell structure used for Gen 3.2 cells.

Figure 1.9: process flow of Si-HJT Gen 2 cells

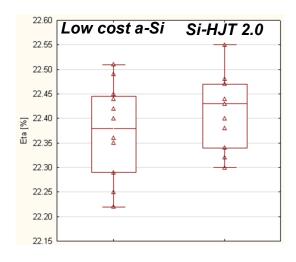

Figure 1.10 shows comparative cell conversion efficiencies between Si-HJT 2.0 cells with (left) and without (right) these new lost cost a-Si processes. We can see that from a statistical point of view there is no impact of these low cost processes on the efficiency that stands to median value of 22.4 %<sup>GT</sup> in both cases. Figures 1.11 shows the efficiency distribution over more than 150 cells with these new processes. It shows that the profile is not a perfect Gaussian as for the Si-HJT 2.0 case (Figure 1.7) and that process uniformity is good. This is confirmed by the small gap between the median and champion cell parameters as shown in Table 1.4.

**Figure 1.10**: efficiency of low cost a-Si process (left) and regular a-Si processes (right). Both are made with the Si-HJT 2.0 structure.

**Figure 1.11**: efficiency distribution of >150 Gen3 .2 cells as measured with the Grid TOUCH contacting unit..

Table 1.4: Gen3.2 cell median and best IV parameters, measured using the PASAN Grid technology.

|        | eff<br>(% <sup>GT</sup> ) | V <sub>oc</sub><br>(mV) | FF<br>(%) | J <sub>sc</sub><br>(mA/cm²) |

|--------|---------------------------|-------------------------|-----------|-----------------------------|

| best   | 22.37                     | 733                     | 79.46     | 38.39                       |

| median | 22.0                      | 728                     | 78.5      | 38.4                        |

The produced Gen 3 cells with low cost a-Si processes have a slightly lower efficiency than the cells from Group 1 (22.2 %<sup>GT</sup>) but are 0.5% absolute above the bifacial efficiency target. Without further notice, these new processes are integrated in all cells manufactured from this point in time.

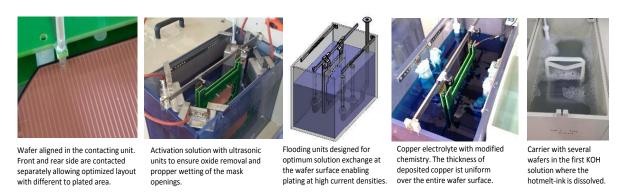

#### Group 3: silver free Si-HJT cells

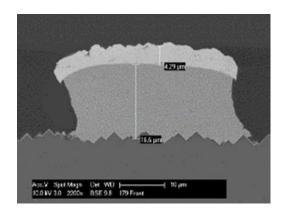

The third and last group of Gen 3 cells is made with the regular Si-HJT structure with front side ITO and the low cost a-Si processes of group 2. The special feature of these cells resides in the metal grids on front and back side. Indeed, as shown in Figure 1.12, the regular screen printed grids made of silver are replaced by copper grids made by electro-plating resulting in high aspect ratio metallic structures (Figure 1.13). The developed process is described in details in a dedicated section in the next chapter but is schematically represented in Figure 1.14.

Figure 1.12: HJT solar cell structure used for Gen 3.3 cells.

**Figure 1.13**: SEM micrograph of a plated finger made of copper and Sn.

We can see that the back end process flow is made of more process steps than regular screen printed grids. Indeed, the one tool process consisting in back side screen printing, paste drying, front side screen printing & paste curing is replaced by a four tool process.

- Metal blanket deposition on both sides by sputtering. This is done together with the the front and back side ITO layers in an additional sputtering chamber.

- Negative masking of the blankets by inkjet deposition of hotmelt on both sides.

- Copper and tin electro plating

- Hotmelt lift-off and cell cleaning in chemical bathes

- Metallic blanket removal by wet-chemical etching

All these processes have been developed and demonstrated at the pilot scale (>20 wafers per hour) by CSEM.

From this very brief description, we can already see that the battle field between silver screen printing and copper plating will be material cost versus processing costs unless there is a significant cell performance advantage for one or the other.

Figure 1.14: process flow of Si-HJT Gen 3.3 plated cells

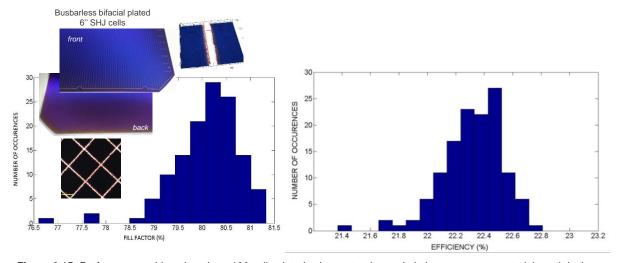

Figure 1.15 presents the efficiency distribution of more than 130 bifacial cells made with copper plating in the pilot line of CSEM. It shows that the distribution is almost Gaussian with a quite narrow spread with all cells with 1% efficiency range. Median efficiency (Table 1.5) is of 22.3 %<sup>GT</sup> and best efficiency is as high as 22.8 %<sup>GT</sup>. Despite the very similar efficiencies compared to Group 1 (Si-HJT 2.0) we can see that the FF is higher by more than 1 %abs for the copper plated cells while the photo-generated

current is very similar and  $V_{oc}$  lower by 5 mV for the copper plated cells. Temptative explanations to these differences may be:

- The higher FF is due to the better electrical conductivity of copper plated fingers as well as possibly better contact resistances of seed layer to ITO than screen printed silver. Plated fingers avoid the trade-off between photo-generated current and FF.

- The current are very similar and can be explained by the lower shadowing losses thanks to the narrower achieved lines by copper plating than with screen printing. This again without a trade-off between electrical and optical properties. Therefore, the current density gained by the Si-HJT 2.0 concept (group 1) is here compensated by narrower lines.

- The slightly lower V<sub>oc</sub> of the copper plated cells may arise from plating process impact. Indeed, the cells are immerged into various chemicals (acidic, alkaline, and solvent) and one of these may impact the unprotected cell edge.

**Figure 1.15**: efficiency distribution of >130 Gen3.3 cells as measured with the Grid<sup>TOUCH</sup> contacting unit..

Table 1.5: Gen3.3 cell median and best IV parameters, measured using the PASAN Grid<sup>TOUCH</sup> technology.

|        | eff<br>(% <sup>GT</sup> ) | V <sub>oc</sub><br>(mV) | FF<br>(%) | J <sub>sc</sub><br>(mA/cm²) |

|--------|---------------------------|-------------------------|-----------|-----------------------------|

| best   | 22.8                      | 734                     | 81        | 38.4                        |

| median | 22.3                      | 729                     | 80.1      | 38.2                        |

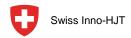

#### Performance from Gen 1 to Gen3 HJT cells

Table 1.6 summarizes the production data from Gen 1 to Gen 3 cells. In general, along the duration of the project the efficiency has been improved from 21.5% <sup>GT</sup> to 22.3% <sup>GT</sup> mean efficiency. More importantly, these results have been achieved while switching from monofacial (Gen 1 @ 21.5% <sup>GT</sup>) to bifacial devices (Gen 3 @ 22.3 % <sup>GT</sup>) that are not the ideal optical structure for champion cell manufacturing. Surprisingly, the main driver for this increase in efficiency has been the photogenerated current that rose by 1 mA/cm² and this despite the bifacial structure. In terms of pure performance, 2 major progresses have been integrated into these solar cells: i) the Si-HJT 2.0 structure and ii) copper plated grids. Both have shown individually their capacity to increase cell efficiency with mass production compatible processes. These two innovations have not been

combined yet, but if technically possible, this may lead to mean efficiency in the  $23\%^{GT}$  range by combining high FF (81%) and both benefits in terms of light management ( $J_{sc}$ = 38.8 mA/cm<sup>2</sup>) and good passivation ( $V_{oc}$  = 735 mV).

Table 1.6: Gen 1 to Gen 3 cell median efficiencies

|        |                            | Eff<br>(% <sup>GT</sup> ) | V <sub>oc</sub><br>(mV) | FF<br>(%) | J <sub>sc</sub> (mA/cm²) |

|--------|----------------------------|---------------------------|-------------------------|-----------|--------------------------|

| Gen1   | monofacial                 | 21.5                      | 725                     | 78.9      | 37.6                     |

| Gen2   | bifacial                   | 21.29                     | 728                     | 78.1      | 37.41                    |

| Gen3.1 | Si-HJT 2.0                 | 22.2                      | 734                     | 78.4      | 38.56                    |

| Gen3.2 | Si-HJT 2.0 low cost a-Si   | 22.0                      | 728                     | 78.5      | 38.4                     |

| Gen3.3 | Low cost a-Si + Cu plating | 22.32                     | 729                     | 80.1      | 38.2                     |

## 1.2 Module production

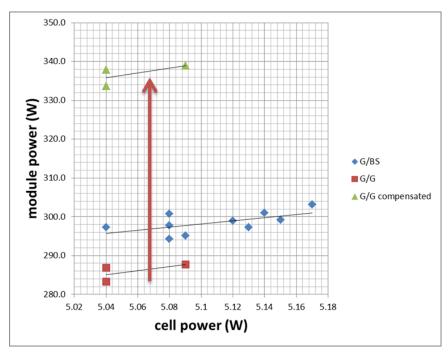

#### 1.2.1 Gen 2 SmartWire Module production

As described earlier in this report, the Gen 2 cells have been manufactured with a bifacial design as opposite to the Gen 1 cells which were exhibiting a full area sputtered metallization on the back side. Even though the Gen 2 cells are bifacial, they can be used either in monofacial modules with a white (or black) back sheet or in a bifacial module with a glass at the back side. In order to evaluate the module power and outdoor performance dependence on module back side design (backsheet or glass) Gen 2 cells have been divided in two groups and integrated in either glass/glass (G/G) bifacial modules or glass/white back sheet (G/BS) modules.

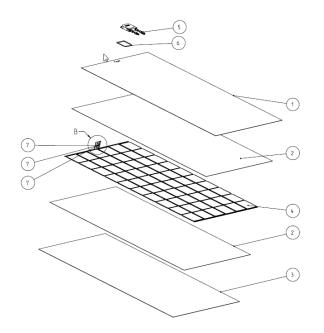

Both modules have a comparable BOM to Gen 1 modules as shown in Figure 1.16:

- ARC glass at front side

- TPO encapsulant

- 18 interconnecting wires with 200 μm core diameter

- InSn low temperature melting alloy coating on the wires

- PET foils to hold the interconnecting wires

- White backsheet with aluminium or glass at back side.

- Centralized junction box

**Figure 1.16:** Gen 1 module layout from front glass (bottom) to back sheet (top).

Figure 1.17: bifacial 60 cell module

Table 1.7 presents the measurement data of the 14 modules manufactured in the SmartWire pilot line at Meyer Burger in Thun. The 10 monofacial modules have been measured under STC using the Dragon Back technique. The remaining 4 bifacial modules have been measured in the same condition but in adding a black background at the back side of the module during measurement, to prevent surrounding light to enter the module and generate extra current.

Table 1.7: Gen 2 module performance under STC

| Module ID | Remark | Cell<br>P <sub>max</sub> (W) | Module<br>P <sub>max</sub> (W) | V <sub>oc</sub> (V) | I <sub>sc</sub> (A) | FF (%)           | CtM loss          |

|-----------|--------|------------------------------|--------------------------------|---------------------|---------------------|------------------|-------------------|

| 15332     |        | 5.04                         | 297.3                          | 43.65               | 9.10                | 74.8%            | -1.7%             |

| 15333     |        | 5.08                         | 300.7                          | 43.79               | 9.12                | 75.3%            | -1.3%             |

| 15334     |        | 5.14                         | 301.0                          | 43.79               | 9.13                | 75.3%            | -2.3%             |

| 15335     |        | 5.08                         | 297.7                          | 43.93               | 9.12                | 74.3%            | -2.3%             |

| 15336     | C/DC   | 5.12                         | 298.9                          | 44.02               | 9.16                | 74.1%            | -2.7%             |

| 15337     | G/BS   | 5.17                         | 303.1                          | 44.28               | 9.14                | 74.9%            | -2.3%             |

| 15338     |        | 5.08                         | 294.2                          | 43.67               | 9.11                | 74.0%            | -3.4%             |

| 15339     |        | 5.09                         | 295.1                          | 43.8                | 9.08                | 74.2%            | -3.4%             |

| 15340     |        | 5.13                         | 297.3                          | 43.84               | 9.10                | 74.5%            | -3.4%             |

| 15341     |        | 5.15                         | 299.1                          | 44.03               | 9.13                | 74.4%            | -3.2%             |

|           |        | average                      | 298.4                          | 43.88               | 9.12                | 74.6%            | -2.6%             |

|           |        | median                       | 298.3                          | 43.82               | 9.12                | 74.5%            | -2.5%             |

| 15344     |        | 5.09                         | 287.7                          | 43.92               | 8.72                | 75.1%            | -5.8%             |

| 15345     | 0/0    | 5.04                         | 286.9                          | 43.84               | 8.70                | 75.2%            | -5.2%             |

| 15346     | G/G    | 5.04                         | 283.3                          | 43.53               | 8.73                | 74.5%            | -6.4%             |

| 15347     |        | 5.04                         | <del>218.2</del>               | 42.41               | 8.75                | <del>58.8%</del> | <del>-27.9%</del> |

|           |        | average                      | 286.0                          | 43.76               | 8.72                | 75.0%            | -5.8%             |

|           |        | median                       | 286.9                          | 43.84               | 8.72                | 75.1%            | -5.8%             |

Without surprise, the highest module power has been achieved with the highest cell power class (5.17W) integrated in a monofacial module. The measured power was as high as 303 W! Overall, the average module power with white back sheet is of 298 W and of 286 W with a transparent glass backside. One of the Glass/Glass modules has been removed from the analysis because of the presence of cracked cells after lamination.

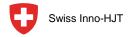

More interesting than the average module power with the 2 different BOM, we should look to the module power output as a function of the cell output power. Indeed, as shown in Figure 1.18, as expected there is a linear dependency between module power and cell power and the glass/glass are well separated from the glass/back sheet modules, but present the same slope. As for bifacial cells, bifacial modules present a pretty low module power since they are measured with a black background without any reflection, either in the module, nor on the cell back side. This results in cell to module (CTM) power losses of about -6% (Table 1.7). The CTM power losses are reduced to -2.5% in the case of white back sheet modules since cell are measured with a black background (pejoration of current density) and a white reflector is added in the module, boosting the photo-generated current. This type of modules with white back reflector is perfect for high power density with single side illumination typically used for roof top integration. On the other hand, when evaluating the performance of bifacial module we have to take into account their bifacial character, i.e. their capability to convert diffused light into electric power, that is not taken into account so far in the standard testing conditions that impose black as a background.

As proposed earlier in this project (see 2015 Report), an easy and well accepted method is to take into account a 20% albedo (20% of AM1.5g illumination at back side) multiplied by the bifaciality of the module (ratio of power generation under STC back:front side):

$$Isc_{comp} = (1 + 0.2 \times Bifaciality) \times Isc_{front}$$

The bifaciality compensated module power by this means is presented in green in Figure 1.18 and represents an average module power of 338 W if integrated in a system with a 20% albedo factor. This power accounts for a module bifaciality of 89% that was measured under STC.

The Gen 2 modules presented here have demonstrated that even if only bifacial cells are used, two types of products can be manufactured: monofacial and bifacial modules. These two types of products even if having the same solar cell engine can target two different markets: i) private rooftop installation with monofacial design and ii) large commercial or utility field with bifacial modules. Both have outstanding performance with either high peak power or very high bifaciality compensated power.

**Figure 1.18:** module power as a function of cell power class for (blue) G/back sheet modules, (red) Glass/Glass modules measured with black back ground and (green) bifaciality compensated glass/glass modules taking into account a 20% albedo and 89% measured bifaciality.

#### 1.2.2 Gen 3 SmartWire Module production

The aim of Gen 2 modules was to introduce the first bifacial modules with a rather standard module balance of material (BOM). For Gen 3 modules, beside novelties at the cell level as described above, new module components are introduced with the aim to reduce the manufacturing costs while increasing the bifacial module power output.

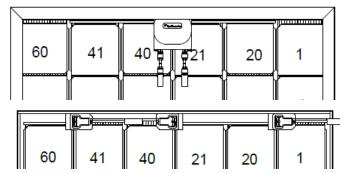

First of all, in order to increase the benefit of the bifacial structure of these modules new junction boxes have been used. These decentralized junction boxes shown in Figure 1.19 present the advantage to reduce the cell overlapping area and hence increase the module bifaciality thanks to reduced light shadowing. The measured bifaciality using these decentralized junction boxes was increased up to 93 %, from the 89% measured with single centralized junction box. All Gen 3 modules are manufactured using this new type of junction boxes.

**Figure 1.19:** (top) single centralized junction box used for Gen 1 and Gen 2 modules and (bottom) multiple decentralized junction box used for Gen 3 modules.

Another module power limitation in the case of Gen 1 and Gen 2 modules is the interconnection wire core diameter. Indeed, the 200  $\mu m$  diameter used for these modules limits the current extraction and impacts the module FF. However, this wire diameter is optimizing the cost to power ratio since the indum based coating of the wire is too costly when used on larger diameter wires. Gen 3 modules are all made with 300  $\mu m$  wires either coated with indium tin (InSn) layer or tin bismuth (SnBi) layer. The SnBi coating makes economically feasible the introduction of 300  $\mu m$  wires (see cost section below) and the goal here is to demonstrate that the low cost SiBn coating can replace the indium based coating without module power loss.

Additionnaly, some monofacial modules with a white back sheet have been manufactured as reference to be compared to Gen 1 and Gen 2 modules.

The module BOM for Gen 3 modules can be then summarized as following:

- ARC glass at front side

- TPO encapsulant

- 18 interconnecting wires with **300** μm core diameter

- InSn or SnBi low temperature melting alloy coating on the wires

- PET foils to hold the interconnecting wires

- Glass at back side or white backsheet with Aluminium.

- De-centralized junction boxes.

Table 1.8 summarizes the combination between the different cell structures and module configuratios. A total of 14 modules have been manufactured including 2 glass / back sheet modules. As shown, no module integrating the copper plated cells has been manufactured so far because of time constrains. However, these modules will be described and analyzed in the complementary report end of 2017 together with the reporting about the long term outdoor monitoring of all module generations.

Table 1.8: Gen 3 modules description for the 4 groups

|   | Cells                       | module          | wires          |

|---|-----------------------------|-----------------|----------------|

| 1 | Si-HJT 2.0                  | bifacial        | InSn 18x300 μm |

| 2 | Si-HJT 2.0                  | White backsheet | InSn 18x300 μm |

| 3 | Si-HJT 2.0                  | Bifacial        | SnBi 18x300 μm |

| 4 | Si-HJT 2.0<br>Low cost a-Si | bifacial        | InSn 18x300 μm |

Table 1.9 displays the measurement data under STC of all modules manufactured with Gen 3 cells. Measurements of bifacial modules have been performed using a white reflecting background and therefore the data cannot be compared to the Gen 2 bifacial.

Table 1.9: Gen 3 modules parameters under STC.

| Module<br>ID | cells         | module         | Cell<br>power<br>(W) | Module power (W) | V <sub>oc</sub> (V) | I <sub>sc</sub> (A) | FF     | CtM    |

|--------------|---------------|----------------|----------------------|------------------|---------------------|---------------------|--------|--------|

| 15371        |               |                | 5.22                 | 292.54           | 44.12               | 8.92                | 74.31% | -6.64% |

| 15372        |               | 00             | 5.23                 | 293.12           | 44.10               | 8.95                | 74.23% | -6.66% |

| 15373        | Si-HJT 2.0    | GG<br>InSn 300 | 5.27                 | 294.57           | 44.16               | 8.93                | 74.72% | -6.84% |

| 15374        |               | 111311 300     | 5.27                 | 295.62           | 44.18               | 8.94                | 74.85% | -6.51% |

| 15375        |               |                | 5.27                 | 294.52           | 44.14               | 8.95                | 74.55% | -6.86% |

|              | Average – 1   |                | 5.25                 | 294.07           | 44.14               | 8.94                | 0.75   | -6.7%  |

|              | Median – 1    |                | 5.27                 | 294.52           | 44.14               | 8.94                | 0.75   | -6.7%  |

| 15377        | C: LLIT 0.0   | GBS            | 5.28                 | 296.00           | 44.23               | 8.92                | 75.09% | -6.60% |

| 15379        | Si-HJT 2.0    | InSn 300       | 5.29                 | 298.20           | 44.25               | 8.94                | 75.40% | -6.03% |

|              | Average – 2   |                | 5.28                 | 294.53           | 44.05               | 8.93                | 0.75   | -7.1%  |

|              | Median - 2    |                | 5.28                 | 296.00           | 44.23               | 8.94                | 0.75   | -6.6%  |

| 15380        |               |                | 5.33                 | 297.1            | 44.256              | 8.887               | 75.54% | -7.09% |

| 15381        | Si-HJT 2.0    | GG             | 5.33                 | 297.52           | 44.256              | 8.91                | 75.45% | -6.96% |

| 15382        | SI-HJ I 2.0   | SnBi 300       | 5.33                 | 299.70           | 44.34               | 8.95                | 75.52% | -6.28% |

| 15383        |               |                | 5.32                 | 298.95           | 44.33               | 8.91                | 75.67% | -6.30% |

|              | Average – 3   |                | 5.33                 | 298.32           | 44.30               | 8.91                | 0.76   | -6.7%  |

|              | Median - 3    |                | 5.33                 | 298.24           | 44.29               | 8.91                | 0.76   | -6.6%  |

| 11405        | 0:1117.00     | 00             | 5.28                 | 297              | 43.89               | 8.95                | 75.51% | -6.25% |

| 21405        | Si-HJT 2.0    | GG             | 5.28                 | 298              | 43.91               | 8.98                | 75.49% | -5.93% |

| 31405        | low cost a-Si | 111311300      | 5.23                 | 295.0            | 43.75               | 8.97                | 75.08% | -5.99% |

|              | Average – 4   |                | 5.26                 | 296.7            | 43.85               | 8.97                | 0.7536 | -6.05% |

|              | Median - 4    |                | 5.28                 | 297              | 43.89               | 8.97                | 0.7549 | -5.99% |

As all modules were measured with a white reflecting background, no differences can be observed between glass/glass bifacial modules and glass/back-sheet monofacial modules. This is shown in Figure 1.20 where all the output power of all modules stand on the same line as a function of the cell power.

**Figure 1.20:** Gen 3 module output power as a function of average cell output power. All modules have been measured with a white reflecting background.

However, when looking closer to the data we can see that the CTM power losses are all about -6.4%, higher than for the Gen 2 glass white back sheet modules (-2.5%), even though comparable to the glass/glass module (-5.8%). But remember that the Gen 2 bifacial modules were measured with black unreflective back ground and the Gen 3 with a white reflecting background. Therefore, we would expect to have CTM power losses comparable to Gen 2 monofacial modules. Moreover, as the interconnecting wires for the Gen 3 modules are thicker (300 vs 200  $\mu$ m) than for Gen 2, we would expect an additional reduction in the FF CTM losses. Unfortunately, this is not observed and the FF CTM losses are in both cases about -4% (relative).

Today, no reasonable explanation can be given to explain this difference between Gen 2 and Gen 3 module CTM losses. These differences have not been observed on the test modules manufactured before this Gen 3 large module series. Investigations are still ongoing and only hypothesis can be drawn for the time being:

- The difference in wafer thickness may be at the origin of the difference in  $I_{sc}$  CTM losses between Gen 2 (+2%rel with 150  $\mu$ m thick wafers) and Gen 3 (-3%rel, 180  $\mu$ m thick wafers).

- However, we have to take into account that the wire diameter is not the same for Gen 2 (200  $\mu$ m) and Gen 3 (300  $\mu$ m) modules, introducing extra shading losses for the second.

- The missing gain in FF when switching from 200 to 300 μm thick wires has no explanation so far. Wire to cell metallization contact could be one possible cause but again, pretests have shown that this was not the case.

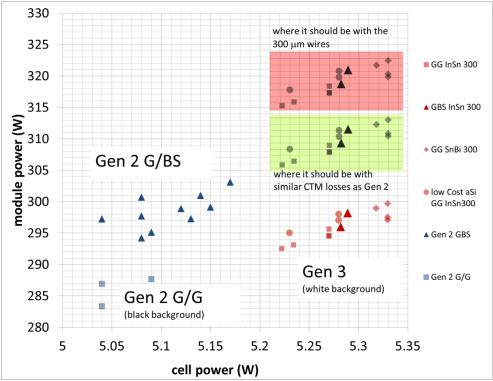

To summarize, as shown in Figure 1.12 the measured module power is not as high as expected. Indeed, the cell power improvement from  $\sim 5.1$  W to  $\sim 5.3$  W was not transformed into module power improvement. With CTM power losses similar to Gen 2 the module power should have been around 310 W (green area in Figure 1.12) and taking into account for the switch from 200 to 300  $\mu$ m thick wires the module power should have be even higher, in the range of 320 W (red area in Figure 1.12). As already said, investigations are ongoing and new modules with similar BOM will be manufactured again to demonstrate these expected power levels.

Figure 1.21: Gen 2 and Gen 3 module power as a function of average cell power. Gen 3 modules should be at least 10 W higher in power.

Nevertheless, when comparing the different module groups when can draw some positive conclusions:

- Indium tin coating on wires can be replaced by tin bismuth without extra CTM losses. This can

be seen in Figure 1.21 where all modules are standing on the line independently to the coating

used on the wire. Moreover, the best module out of this Gen 3 production is a module with

bismuth tin coating.

- The low cost a-Si processes do not impact the module power as well. It could even improve by

~1W the module power as shown in Figure 1.20, but more statistics is needed to have a more

reliable statement.

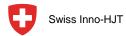

Figure 1.22 summarizes all modules and cell output power from Gen 1 to Gen 3 modules that have been developed and manufactured within the Swiss Inno-HJT project. Starting from the Gen 1 monofacial cells and modules, it can be seen that a huge progress has been realized. First, managing the transition from monofacial to bifacial cells generating a gain in monofacial module output power of more than 15 W. Second, the introduction of new technologies and processes at the cell level resulted in an important gain in power output at the cell level. Bifacial cells with more than 5.3 W were manufactured with a narrow distribution. However, for still unknown reasons, we were not able to convert this improvement in cell power output into module power improvement. Preliminary tests were successful and investigations are still ongoing to understand and solve this issue

Figure 1.22: average power output of cells and modules produced within the Swiss Inno-HJT project. The Gen 2 GG modules (light red bar) are the only one measured whithout white reflecting background and therefore direct comparison with the other modules is difficult. The gen 1 cells (green diamond) are the only monofacial cells presented here.

A total of 39 good modules have been produced within the Swiss Inno-HJT project, cumulating a peak power output of 11'353 Wp. Thirty of these modules together with 10 reference modules have been installed for outdoor monitoring in Hauterive, Neuchâtel (see Figure 2.13). Data are discussed in a separate section in this report and will be consolidated by end of 2017 after 1 full year of outdoor acquisition for all Generations of modules.

Figure 1.23: outdoor installation of 40 module, 10 reference and 30 modules produced within the Swiss Inno-HJT project

### 1.3 Manufacturing cost analysis

Manufacturing costs for the different cells and module configuration presented above have been evaluated. Since material costs have dramatically dropped mid 2016 because of production over capacity, the figures presented in this section cannot be fairly compared to the Gen 1 module manufacturing costs that have been presented in the 2015 report. As a reminder, the Gen 1 manufacturing costs were  $0.64 \, \text{CHF/W}_D$ , hitting the  $0.65 \, \text{CHF/W}_D$  Swiss Inno-HJT cost target.

The cost analysis presented here take into account the latest material costs that are viable for the producer at least on mid-term. As an example, monocrystalline wafer can be found at prices as low as 0.9  $\cite{CHF}$ ) per piece for standard 180  $\mu$ m thickness. End of 2015 this price was at 1.1  $\cite{CHF}$  per piece. We decided not to be too optimistic and we have selected a price that is reliable on a more long term target, i.e. 1  $\cite{CHF}$  per piece for a standard thickness.

Cost calculations were done with the following assumptions:

- Production capacity of about 200 MW, corresponding to 2 production lines.

- Production site in Asia (China, Malaysia,...)

- Depreciation duration of equipment of 7 years (building 30 years).

- Interest rate of 0% (generally agreed to compare different technologies)

- Wafer cost based on latest announcement of wafer manufacturer with target price of 0.7 \$ per piece for as cut thickness of 130 μm in 2020.

Table 1.10 presents the manufacturing costs for different configurations with costs separated for wafer, cell and module parts. As for the module power comparison in the previous section, only modules measured with a white reflecting background are presented in this table. The last column presents what could be a target for HJT modules in 2020.

First of all, we can note that all steps, wafers, cells and modules have their importance in reducing the costs. The wafers, as discussed in the previous paragraph have a major impact. For Gen 2 modules, the used thickness was 150  $\mu$ m, 30  $\mu$ m thinner than for Gen 1 and Gen 3 modules accounting for a ~10% module cost reduction. In the future, 130  $\mu$ m as cut thickness will be available from wafer manufacture thanks to diamond wire cutting technology and they will be key to further reduce the module costs.

About the cell cost, there has been an important decline in production costs with the introduction of Si-HJT 2.0 cell structure, -20% cell manufacturing costs, and low cost a-Si processes, -12%. A total of 30% cell manufacturing cost reduction has been achieved, accounting for 10 CHF (-8%) module cost. Further, improvements in terms of cell manufacturing are foreseen mostly in terms of equipment cost reduction by the introduction of new manufacturing technologies. These should be ready at the horizon 2020 and offer about 25% cost reduction in cell manufacturing.

Despite the difficulties encountered to transfer the increased power output of the Si-HJT2.0 cells into the module, a major milestone has been achieved with the successful introduction of the tin bismuth coating on the wire. It has been shown that no power difference between the original InSn coating and the new SnBi was observed, but more importantly, this material substitution reduces considerably the wire costs. Indeed, 300 µm core wire diameter can be used with the SnBi coating instead of the 200 µm InSn wire together with a cost reduction of about 2 CHF per module. Overall, it is now possible to shift the module structure from monofacial glass/backsheet to bifacial glass/glass while reducing the module manufacturing costs from 40.6 CHF to 39 CHF per module. Further progresses on both the equipment and the BOM will reasonably lead to a module manufacturing cost reduction of about 10%.

Table 1.10: cost analysis of Gen 2 and Gen 3 modules. Gen x represents an achievable cost target.

|                                     | Gen 2                          |                               | Ge                             | n 3                           |                               | Gen x                         |

|-------------------------------------|--------------------------------|-------------------------------|--------------------------------|-------------------------------|-------------------------------|-------------------------------|

| Cell type                           | Si-HJT<br>bifacial             | Si-HJT 2.0                    | Si-HJT 2.0                     | Si-HJT 2.0                    | Si-HJT 2.0<br>Low cost a-Si   | Si-HJT 2.0<br>Low cost a-Si   |

| Module type                         | G/BS 200 μm<br>InSn<br>@ 298 W | G/G 300 μm<br>InSn<br>@ 294 W | G/BS 300 μm<br>InSn<br>@ 297 W | G/G 300 μm<br>SnBi<br>@ 298 W | G/G 300 μm<br>InSn<br>@ 297 W | G/G 300 μm<br>SnBi<br>@ 315 W |

| N type mono c-Si wafer<br>per wafer | 0.82 CHF<br>(150 μm)           | 1 CHF<br>(180 μm)             | 1 CHF<br>(180 μm)              | 1 CHF<br>(180 μm)             | 1 CHF<br>(180 μm)             | 0.7 CHF<br>(130 μm)           |

| Cell manufacturing per cell         | 0.51 CHF                       | 0.4 CHF                       | 0.4 CHF                        | 0.4 CHF                       | 0.35 CHF                      | 0.26 CHF                      |

| Module manufacturing per module     | 40.6 CHF                       | 47 CHF                        | 44 CHF                         | 39 CHF                        | 47 CHF                        | 35 CHF                        |

| Total module cost<br>per module     | 121 CHF                        | 131 CHF                       | 128 CHF                        | 123 CHF                       | 128 CHF                       | 93 CHF                        |

| CHF/Wp                              | 0.41 CHF/Wp                    | 0.45 CHF/W <sub>p</sub>       | 0.44 CHF/W <sub>p</sub>        | 0.41 CHF/W <sub>p</sub>       | 0.43 CHF/W <sub>p</sub>       | 0.30 CHF/W <sub>p</sub>       |

Overall, similar total manufacturing costs per module have been reached for both monofacial (121 CHF) and bifacial (123 CHF) modules. The resulting cost per watt is by far below the target and reaches 0.41 CHF/W<sub>p</sub>. Of course, the technologies and processes developed within the Swiss Inno-HJT project helped greatly to achieve this target but this drastic decrease over 2016 from 0.64 down to 0.41 CHF/W<sub>p</sub> was made possible as well because of the material cost decrease. Taking the best of each module, we can state that it should be possible today to demonstrate a 310 W with manufacturing cost of about 110 CHF by using 150  $\mu$ m thick wafers, Si-HJT 2.0 cells with low cost a-Si processes and 300  $\mu$ m SnBi interconnecting wires, thus achieving <0.36 CHF/W<sub>p</sub>. Looking at the 2020 horizon, access to 130  $\mu$ m thick as cut wafers, further investment reduction both at the cell and module manufacturing level and further cost down thanks to material utilization together combined with a reasonable 315 W module power would make possible to achieve module production cost below 0.3 CHF/W<sub>p</sub>.

## Development activities

In parallel to the preparation and production of the Gen 2 and Gen 3 cells and modules, R&D efforts have been made to improve cost and performance along the full value chain. In this section, some highlights are presented.

#### 2.1 Thin wafers

Using thinner wafers than standard thickness poses challenges for cell processing due to changed mechanical properties that cause increased flexibility but at the same time increased wafer breakage and for cell performance. If both challenges are mastered sufficiently thickness reduction should translate into device cost reduction.

During the project the impact of wafer thickness on mechanical yield was studied for manual and automated wafer handling. Since manual handling yield strongly depends on experience we have observed an expected yield loss going to thinner wafers. While breakage rates are not considerably higher for wafers with an as cut thickness of down to 130µm, which translates into cell thickness of around 110µm, the breakage rate increases notably when cell thicknesses drops below 100µm.

Within the project devices as thin as 50µm have been processed, where the mechanical yield was typically only around 50%.

Monitoring the mechanical yield an automated production line revealed also that processing of wafers with as cut thicknesses of 130µm, i.e. 110µm precursor thickness after wet chemical precursor preparation did not lower mechanical yield. Even processes with high mechanical load on the wafers especially the screen printing did not turn out to be critical in terms of mechanical and electrical yield. The process most critical for as cut wafers thinner than 130µm is the wet chemistry, where increased wafer flexibility caused issues with wafers sticking due to adhesion forces when the wafers are removed from the process liquid.

Yield issues were observed with individual automation stations that sort wafers in and out of carriers, however, those issues were observed not to depend on wafer thickness down to 130µm. For wafer thinner than 130µm an adaptation of the wafer handling in the wet chemistry process would be required to allow high yield processing, the loads on the cell precursors during screen printing needs to be carefully adjusted for precursor thicknesses below 100µm even if successful printing on precursors as thin as 50µm has been demonstrated.

In conclusion cell processing with as cut wafers as thin as 130µm was investigated and found to operate at high yield without thickness related issues.

Cell performance will ideally change little or even not at all when thinner wafers are used for processing. It has been shown that traditional diffusion type silicon cells and even modern rear side passivated (PERC) cells show decline in cell performance when thinner wafers are used. The challenge here is to compensate the reduced silicon absorber volume of the cell by high quality surfaces that minimize losses at the same, which is a key signature for heterojunction technology. HJT cells with different thickness have been processed and characterized.

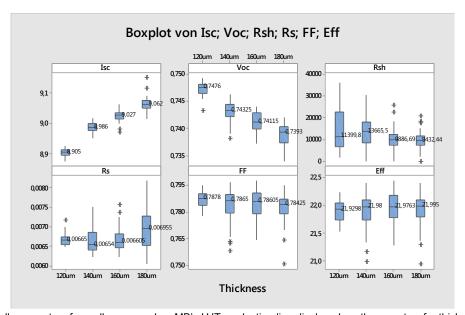

Figure 2.1: HJT cell parameters for cells made from different wafer thicknesses as a function of cell thickness.

As shown in Figure 2.1, as expected Voc increases with decreasing cell thickness due to a very effective surface passivation while Jsc decreases due to the reduced absorber volume and implied optical losses. The FF is nearly independent of thickness and as a result cell efficiency changes only little with the latter.

Figure 2.2: Cell parameters from ell processed on MB's HJT production line displayed vs. the as cut wafer thickness. Final cell thickness is around 20µm less.

Similar results were obtained from test lots run on automated production tools that exhibited a practically thickness independent performance for cell thicknesses down to 100µm.

One of the most effective ways towards cost saving is reduction of wafer thickness that allows for a lower wafer costs and thus impacting directly all subsequent cost structures. Wafering for mono crystalline silicon by diamond wire has found wide spread industrial application since 2013. While at the beginning of the project the standard diameter for the diamond wire was 100µm, today the saws with their respective wire management system facilitate handling of wires as thin as 60µm as applied and developed in MB's R&D. Combined with a controlled cut of thin wafers this reduces the so called kerf and thus allows to yield more wafers from the same silicon ingot crystal. The standard wafer thickness at the beginning of the project was 180µm while current cell production at Meyer Burger uses wafers with a thickness of 135µm. Owing tool development for the saws not only the capability of handling thinner core-wire was developed but also the throughput, i.e. the productivity of the tool was considerably increased to more than twice. The cost reduction stemming from these advancements in wafering translate to approximately 30% for a conservative calculation to approximately 40% for a more realistic estimate with the above given numbers.

This trend is reflected in current market spot prices; however the standard market wafer thickness with now around 170µm is still considerably much thicker than above mentioned 135µm as cut wafers.

With processing yield, cell efficiency and wafer cost issues address as above it can be concluded that thin wafers can now be used in MB's HJT production with practically no performance loss and a large cost advantage. The cost advantage translates 1 to 1 to cell and module costs.

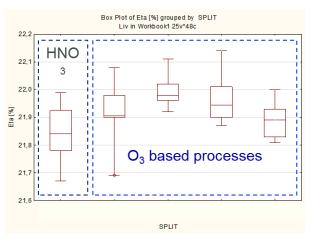

### 2.2 Ozone process

At the beginning of the Swiss Inno-HJT project the wet chemistry wafer texturing and cleaning process was based on hydrogen peroxide and nitric acid. Both are used because of their oxidising power and the later in high concentration while the first is volatile and needs a constant feeding to the process.

Therefore, these chemicals are the cost drivers in the wet processing and they require increased safety measures for stock keeping and application.

An alternative chemical with high oxidising power know from semiconductor industry which is finding more and more application also in the PV industry is ozone  $(O_3)$ . The ozone is generated, mixed into the process liquid and destroyed on-side. It has the advantage of being virtually contamination free being generated from much less costly oxygen in gas form  $(O_2)$ , which is much less demanding and dangerous in storage. While hydrogen peroxide and nitric acid need to be applied in high concentrations in the %-range, ozone is dissolved and very effective in much lower concentrations of the ppma-range.

With the much favourable cost structure, the ozone-based chemistry needs to perform on the same level. This was developed, optimised in many single aspects and ultimately achieved for an entirely ozone-based wet chemical process replacing hydrogen peroxide and nitric acid entirely.

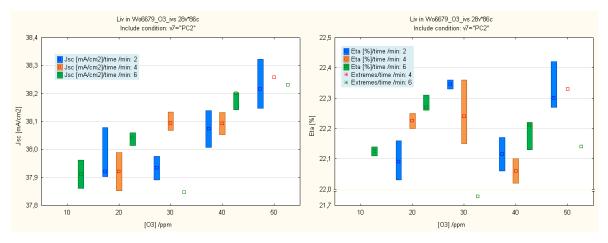

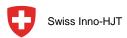

Figure 2.3: Short circuit current and efficiency of HJT cells as a function of ozone concentration [O<sub>3</sub>]

In the wet chemical processing three major oxidising process steps are applied; an oxidation for the incoming wafers, cleaning the wafer surfaces from coarse contamination by destroying surface attached organics, an oxidation before texturing and a final oxidation for ultimate surface cleaning.

Above pictured influence of pre-texturing oxidation as a function of the ozone process step shows that the texturing quality can be improved by ozone and thus the cells yield higher current and efficiency  $\eta$  that also surpasses level of the previously hydrogen peroxide based process step.

The final surface clean is a key process step that determines how well the surface can be passivated. The development of this process step has obtained most attention. By developing ozone based chemistry we were able to further improve the previously nitric acid based surface cleaning.

Furthermore, due to the more effective cleaning it is now possible to omit process steps that needed to be applied previously, making not only the process much more cost effective by reducing the running costs, but also allowing to reduce size and cost of the wet bench thus lowering the financial market entry barrier.

Calculation for the reduction of the cost of ownership when switching to ozone chemistry is in the range of 30-40%. Cost savings on the wet bench tool and new processing with reduced process steps should translate to a further cost saving of around 20% for the wet processing.

Figure 2.4: Efficiencies of HJT cells for various surface conditions, i.e. final clean processes

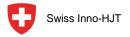

### 2.3 Advanced metallization

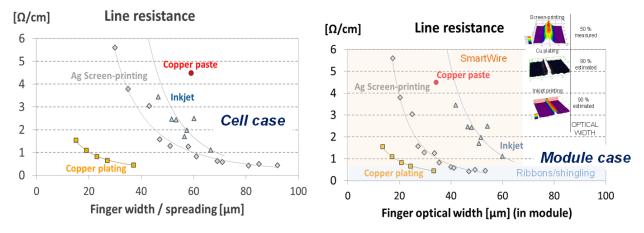

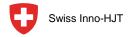

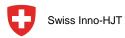

An intrinsic process limitation of HJT solar cells is the requirement for a low temperature processing consecutively to the a-Si:H layers depositions, to not degrade its passivation properties. This imposes the use of Ag pastes with curing temperatures typically below 250 °C. The printing of state-of-the-art low-temperature cured Ag pastes yields Ag lines with bulk resistivity with 6 to 10 ×10<sup>-6</sup> Ohm·cm, about a factor 2 to 3 higher than state-of-the-art metallization based on firing-through of high-temperature Ag pastes. The higher Ag line bulk resistance for HJT solar cells when compared to homojunction solar cells therefore imposes economical and performance limitations for standard H-pattern metallization with 2 to 5 busbars: more Ag is required to achieve similar line resistance and lines with higher resistivity or larger dimension have to be employed. Using state-of-the-art low-temperature cured Aq pastes for H-pattern cells with 3 to 5 busbars, improved performance can for instance be achieved using multiple printing, and typical laydown mass of Ag of 180 mg per side can be considered, representing, for an assumed Ag price of 500 \$/kg, a metallization cost of 9 \$cts/cell, and for a cell > 22.5 % typically ~ 1.68 \$cts/Wp per side, or 3.36 \$cts/Wp for a bifacial cell (as assumption and simplification, Ag paste cost is considered equivalent to Ag price, taken at 500 \$/kg in this report). To overcome this cost and performance limitation due to the metallization, two main routes were addressed in the frame of the Swiss Inno HJT project, with strong focus on:

- Relaxing the constraints on the metal grid conductance by using multi-wire interconnection: this enables for development and integration of fine-line printing of low temperature cured Ag (providing performance gain and cost reduction), and of alternative material and deposition techniques;

- Enhancing the metal grid conductance by switching to copper plated fingers: this approach was studied for varied modules configurations, from standard busbar/ribbon to shingling direct cell interconnections, and multi-wires.

Overall, a very complete metallization and interconnection platform was set-up at CSEM for the *Swiss Inno-HJT* project, providing CSEM with key expertise and know-how, with flexible fabrication equipment and high performance processes, and with detailed characterization and simulation tools, for the metallization and the interconnection of cells and modules using advanced industrial technologies.

Figure 2.5: CSEM platforms for metallization and interconnection developed in Swiss Inno HJT project.

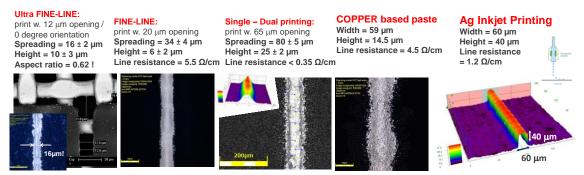

#### **Printing developments**

In the case of busbar/ribbon interconnection design, the cell metal fingers should demonstrate a line resistance <  $0.5~\Omega/cm$  to not yield resistive losses. Screen-printing parameters and pastes were first optimized to achieve the line resistance target with a minimum of Ag usage and with minimum line width. All these developments, taking into account recent progress of Ag pastes, lead to:

- 5 busbars cell, printed fingers properties: line spreading of 70 to 80 μm, line resistance of Ag <  $0.5 \Omega$ /cm, deposited weight of 220 mg for bifacial cells, corresponding to ~ 11 \$cts/wafer.

With the use of SmartWire technology, the constraint on the conduction of the cell metal fingers is strongly relaxed, and typical line resistance of up to 5-8  $\Omega$ /cm does not yield resistive losses. A strong focus was therefore set in the project on the development of fine-line printing of low-temperature cured Ag pastes. By working on the evaluation of different pastes, different screens, openings, and different printing parameters, fine-line printing and ultra-fine line printing could be achieved:

- SmartWire interconnection, fine-line: line spreading of 30 to 40  $\mu$ m, line resistance of Ag < 6  $\Omega$ /cm, deposited weight of 60 mg for bifacial cells, ~ 3 \$cts/wafer.

- SmartWire interconnection, ultra-fine-line: line spreading down to 16 μm, achieved with advanced mesh orientation/design, screen costs then overcomes Ag savings, not competitive.

In addition, developments were conducted on alternative printed materials and printing technologies. The screen-printing of Copper based paste cured at low temperature was evaluated, and the inkjet printing of Ag inks cured at low temperature was developed. The properties of the printed lines are summarized in Figure 2.6. At present stage, the copper based paste does not provide sufficient costs reduction with respect to Ag paste, while the Ag inks used in inkjet printing have high costs, so that the two alternative materials and technologies evaluated are not yet at competitive level with respect to fine-line printing of Ag lines.

Figure 2.6: Summary of properties of lines printed at CSEM following developments on screen-printing and inkjet-printing.

#### **Plating developments**

A strong focus was set in the project on the full development of materials, processes, technologies and fabrication equipment for the definition of a plating technology for bifacial silicon heterojunction solar cells, compatible with line dimensions  $< 50 \mu m$ . Over the course of the project, the needed technologies have been developed, optimized and matured, as detailed in Table 2.1.

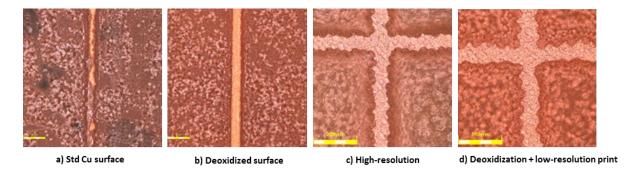

In the metallization of HJT cells by electroplating, patterning is needed to define the front and back metallic grid geometries. This step creates an insulating layer on the seed-layer with small cavities where the subsequent growth of the metallic finger will occur. In the Swiss Inno HJT project, an industrially compatible process based on inkjet printing of an insulating hotmelt ink was chosen. In this process, the hotmelt is heated until becoming liquid inside the printing head and then solidifies when reaching the substrate surface. A crucial point in the development of printing recipes is the determination of the resolution. Indeed, a high printing resolution although allowing the realization of small geometries leads to an important ink consumption and to long printing time. Here, this tradeoff between the printing speed, the ink consumption and the minimal feature size achievable is managed by using a two steps approach for the front-side patterning: First, a low-resolution print defines the rough shape of the finger by creating openings in the 200 µm range [see Fig. 2.7 a)]. This process is made by heating the substrate at 50°C in order to promote the ink droplets spreading thus allowing to connect to each other. Then, a second print is carried out by using this time a high resolution print which accurately defines the finger edges [Fig. 2.7 b)]. Therefore, by using this two steps approach, extremely narrow geometries as small as ~30 µm can be obtained while maintaining a low hotmelt consumption. At the rear-side, due to the "mesh" geometry featuring lines at 45° and as the optical constraints are relaxed compared to the front-side, a single print approach is used achieving geometries in the 60 um range as shown in Fig. 2.7 c), printing at lower-resolution (i.e. requiring less printing time) is investigated. However, if directly used on a bare Cu surface, such low-resolution print leads to clogged cavities as seen in Fig.2.8. To control the flow of the hotmelt ink on the Cu surface, the native oxide of the Cu seed-layer can be removed. This results in a significant improvement of the hotmelt cavities edges as seen on Fig. 2.8. In the framework of the Swiss Inno HJT project, this process was applied at the back-side of the cell therefore reducing the processing time and the hotmelt ink consumption [Fig. 2.8]. This process can be as well applied at the front side and demonstrates the feasibility of opening of ~30 µm thus suppressing the need of a second print. However, the sidewalls achieved with this process will not be as vertical as in the standard two-step approach resulting in wider fingers if a thick Cu layer is grown.

**Table 2.1:** Summary of technologies developed from cell to module for efficient, reliable and cost competitive plating based metallization for silicon heterojunction solar cells.

| Process,                                                                | Developments                                                                                                                                                                                                                                                                                                                  | Focus year 3                                                                                                                                      | Achievements                                                                                                                                                                                                                                                     |