Schweizerische Eidgenossenschaft Confédération suisse Confederazione Svizzera Confederaziun svizra Department of the Environment, Transport, Energy and Communication DETEC

Swiss Federal Office of Energy SFOE Energy Research

Final report 30.01.2019

# Mission- & Time-Critical Medium Voltage Broadband Power Line Communications for Synchrophasor Applications in the Distribution Grid

© HSLU 2018

Lucerne University of Applied Sciences and Arts

# HOCHSCHULE

Engineering and Architecture FH Zentralschweiz

Date: 30 January 2019

Place: Horw

#### Publisher:

Swiss Federal Office of Energy SFOE Research Programme Grids CH-3003 Bern <u>www.bfe.admin.ch</u> <u>energieforschung@bfe.admin.ch</u>

#### Agent:

Lucerne University of Applied Sciences and Arts (HSLU) Technikumstrasse 21, CH-6048 Horw www.hslu.ch

#### Author:

Stephen Dominiak, Lucerne University of Applied Sciences and Arts, <u>stephen.dominiak@hslu.ch</u> Ulrich Dersch, Lucerne University of Applied Sciences and Arts, <u>ulrich.dersch@hslu.ch</u>

SFOE head of domain:Dr Michael Moser, michael.moser@bfe.admin.chSFOE programme manager:Dr Michael Moser, michael.moser@bfe.admin.chSFOE contract number:SI/501504-01

The author of this report bears the entire responsibility for the content and for the conclusions drawn therefrom.

### Summary

Worldwide, increasing pressure is being placed on the electric grids and, in particular, the Medium Voltage (MV) grids due to the increasing introduction of Distributed Energy Resources (DER). Grids must be able to accommodate new energy flow patterns in a more dynamic environment. This leads to the need not only for increasing the monitoring of the grid, but also to actively detect and mitigate the influence of potential faults in the grid. This requires Mission-and-Time-Critical (MTC) applications such as Phasor Measurement Units (PMU) measuring synchrophasors or Line Differential Protection (LDP). However, the communication requirements of such applications (high availability, low latency) provide a significant challenge to the communication infrastructure.

The motivation behind this project has been the development of a new Grid Monitoring & Automation (GMA) solution which takes advantage of the full potential of Broadband Power Line Communications (BPL) for enabling GMA applications in the MV grid. The major advantage provided by a MV-BPL solution is the low-cost communications infrastructure as the MV grid serves also as the communications medium. This goal has been achieved by adapting the MV-BPL technology in order to enable MTC functionality including time synchronization, higher availability and low-latency. Optimizations to the MV-BPL protocol have been aided through a model-based design approach in a simulation environment. The optimizations have been realized on a series of prototypes and tested within a laboratory environment as well as on a MV overhead test line at HSLU. Testing has shown that the developed MTC-MV-BPL solution can meet the strict requirements of LDP and PMU applications. Further field trials with the MTC-MV-BPL technology will now be performed in a follow-up "Pilot and Demo" project partially funded by SFOE.

## Résumé

De manière globale, une pression grandissante est appliquée sur les réseaux électriques, et en particulier sur les réseaux de moyennes tensions (MT). La cause étant l'introduction croissante des ressources énergétiques distribuées (RED). Ainsi, les réseaux doivent être capables de s'adapter à de nouveaux modèles de flux d'énergie dans un environnement plus dynamique. Il est donc nécessaire d'augmenter la surveillance du réseau ainsi que d'activement détecter et réduire l'influence de potentielles erreurs dans les réseaux électriques. Ces genres de contrôles requièrent des applications telles que des unités de mesure de phaseurs (Phasor Measurement Unit - PMU) qui permettent, entre autres, la protection différentielle de lignes. De façon générale, les exigences de telles applications, grande disponibilité et courte latence, induisent un grand défi pour les infrastructures de communication.

La motivation derrière ce projet a été le développement d'une nouvelle solution pour la surveillance et l'automatisation des réseaux électriques, basée sur les avantages de la communication par courant porteurs en ligne (Broadband Power Line Communication - BPL) qui permettent l'intégration d'applications de surveillance et d'automatisation dans les réseaux MT. L'avantage majeur de la technologie BPL, utilisée dans les réseaux de moyennes tensions (BPL-MT), est le bas coût des infrastructures de communication, le réseau électrique existant servant également de moyen de communication. L'objectif a été atteint en adaptant la technologie BPL-MT, en activant les fonctionnalitées MTC (Mission-and-Time-Critical) lequelles incluent la synchronisation d'horloge, une disponibilité accrue ainsi qu'une latence réduite. Les optimisations apportées au protocole BPL-MT ont été réalisées, dans un premier temps, à l'aide d'une approche conceptuelle basée sur un model exécuté dans un environement de simulation. Par la suite, des prototypes ont été élaborés, puis testés en laboratoire ainsi que sur une ligne de test MT à l'HLSU. Les tests ont montré que la solution développée, BPL-MT-MTC, couvre les exigences requises pour la protection différentielle de lignes et <sub>3/74</sub>.

des applications utilisant des PMU. De plus amples essais utilisant cette technologie, BPL-MT-MTC, seront effectués lors du prochain projet, pilote et de démonstration, partiellement fondé par SFOE.

## Zusammenfassung

Weltweit wird durch die zunehmende Einführung von dezentralen Energiequellen ein wachsender Druck auf die elektrischen Netze und insbesondere auf die Mittelspannungsnetze (MS-Netz) ausgeübt. Die Netze müssen in der Lage sein, neue Energieflussmuster in einem dynamischen Umfeld aufzunehmen. Daraus ergibt sich die Notwendigkeit, nicht nur die Überwachung des Netzes zu erhöhen, sondern auch den Einfluss potenzieller Störungen im Netz aktiv zu erkennen und zu minimieren. Dies erfordert Mission- und Time-Critical (MTC) Anwendungen wie Phasor Measurement Units (PMU), die Synchrophasoren messen, oder Line Differential Protection (LDP). Die Kommunikationsanforderungen solcher Anwendungen (hohe Verfügbarkeit, geringe Latenzzeiten) stellen jedoch eine grosse Herausforderung für die Kommunikationsinfrastruktur dar.

Die Motivation für dieses Projekt war die Entwicklung einer neuen Grid Monitoring & Automation (GMA) -Lösung, die das volle Potenzial der Broadband Power Line Communications (BPL) für GMA-Anwendungen im MS-Netz nutzt. Der grosse Vorteil einer MS-BPL-Lösung ist die kostengünstige Kommunikationsinfrastruktur, da das MS-Netz selbst als Kommunikationsmedium dient. Dieses Ziel wurde durch Anpassungen der MS-BPL-Technologie erreicht, welche MTC-Funktionen wie Zeitsynchronisation, hohe Verfügbarkeit und niedrige Latenzzeiten ermöglichen. Optimierungen des MS-BPL-Protokolls wurden in einer Simulationsumgebung durch den Model-Based Design Ansatz realisiert. Die Umsetzung erfolgte anhand mehrerer Prototypen, welche in Laborumgebung sowie auf einer MS-Freileitung an der HSLU getestet wurden. Die Tests haben gezeigt, dass die entwickelte MTC-MS-BPL-Lösung die hohen Anforderungen von LDP- und PMU-Anwendungen erfüllen kann. Weitere Feldversuche mit der MTC-MS-BPL-Technologie werden nun in einem vom BFE mitfinanzierten Pilot- und Demonstrationsprojekt durchgeführt.

# Contents

0

| 1     | Introduction                                       | 11                 |

|-------|----------------------------------------------------|--------------------|

| 1.1   | Overview                                           | 11                 |

| 1.2   | Medium Voltage Broadband Power Line Communications | 12                 |

| 1.3   | Challenge                                          | 14                 |

| 2     | Goal of Project                                    | 17                 |

| 2.1   | Main Goal                                          | 17                 |

| 2.2   | Report Outline                                     | 17                 |

| 3     | Power Line data bUS (PLUS) Technology              | 18                 |

| 3.1   | Introduction to Power Line Communications (PLC)    | 18                 |

| 3.2   | Challenges of PLC                                  | 18                 |

| 3.3   | Power Line data bUS (PLUS)                         | 21                 |

| 3.4   | PLUS Modem Architecture                            | 23                 |

| 3.5   | PLUS-TimeSync                                      | 24                 |

| 4     | PLUS Smart Grid Design                             | 27                 |

| 5     | Latency Optimization                               | 29                 |

| 5.1   | Latency in Communications Systems                  | 29                 |

| 5.2   | Latency in PLUS                                    | 31                 |

| 5.3   | FFT Latency Reduction                              | 33                 |

| 5.3.1 | Introduction                                       | 33                 |

| 5.3.2 | FFT Processor Architecture                         | 33                 |

| 5.3.3 | General Purpose FFT Core                           |                    |

| 5.3.4 | Evaluation on FPGA                                 | 35                 |

| 5.3.5 | Summary                                            |                    |

| 5.4   | Turbo Decoder Latency Reduction                    |                    |

| 5.5   | Higher Order Modulation                            | 41                 |

| 6     | Network Support                                    | 43                 |

| 6.1   | Overview                                           | 43                 |

| 6.2   | Multi-hop MAC Protocol                             |                    |

| 6.3   | Multi-hop Routing Support                          |                    |

| 6.4   | Multi-channel Support                              |                    |

| 6.5   | Interface to Smart Grid Application Devices        | 50                 |

| 7     | Development Process Optimization                   | 52                 |

| 8     | MV-BPL Security Analysis                           | 54                 |

| 8.1   | Introduction                                       | 54                 |

| 8.2   | Authentication                                     |                    |

| 8.3   | Encryption                                         | 55 <sub>5/74</sub> |

| 8.4      | Data Integrity                                      | 55 |

|----------|-----------------------------------------------------|----|

| 8.5      | Protection Against Replay Attacks                   | 57 |

| 8.6      | Physical Access Control                             | 58 |

| 8.7      | Anti-Jamming Techniques                             | 58 |

| 8.8      | Protection Communication Supervision (PCS)          | 59 |

| 8.9      | Summary                                             | 59 |

| 9        | PLUS-Smart Grid Prototypes                          | 60 |

| 10       | Laboratory Testing                                  | 63 |

| 10.1     | Introduction                                        | 63 |

| 10.2     | Test Setup A – HSLU/BKW Smart Grid Laboratory       | 63 |

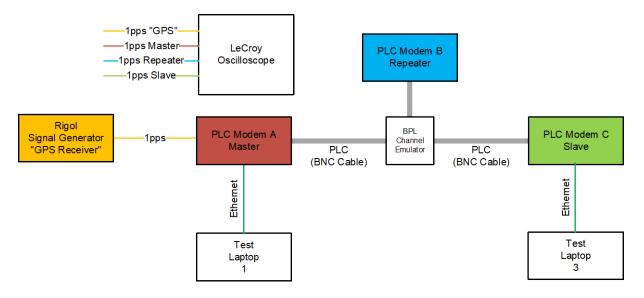

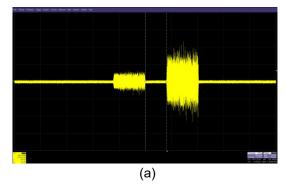

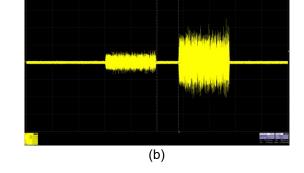

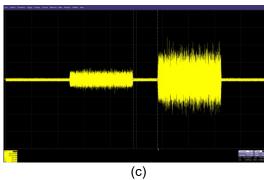

| 10.3     | Test Setup B – HSLU BPL Test Laboratory             | 66 |

| 10.4     | Test Setup C - HSLU Medium Voltage Overhead Testbed | 69 |

|          | Conclusion and Outlook                              |    |

| 11       | Conclusion and Outlook                              | 71 |

| 11<br>12 | Publications                                        |    |

# List of abbreviations

| AC      | Alternating Current                                  |

|---------|------------------------------------------------------|

| ADC     | Analog-to-Digital Converter                          |

| AES     | Advanced Encryption Standard                         |

| AFE     | Analog Front End                                     |

| AMI     | Automated Metering Infrastructure                    |

| ARP     | Address Resolution Protocol                          |

| ARQ     | Automated Repeat Request                             |

| ASIC    | Application-Specific Integrated Circuit              |

| AWGN    | Additive White Gaussian Noise                        |

| BDS     | Beacon Data Service                                  |

| BER     | Bit Error Rate                                       |

| BKW     | Bernische Kraftwerke AG                              |

| BPL     | Broadband Power Line Communications                  |

| BPSK    | Binary Phase-Shift Keying                            |

| BRAM    | Block-RAM                                            |

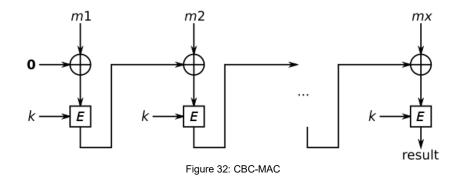

| CBC     | Cipher Block Chaining                                |

| CF      | Classical Flooding                                   |

| CFP     | Contention Free Period                               |

| СР      | Contention Period                                    |

| CPU     | Central Processing Unit                              |

| CRC     | Cyclic Redundancy Check                              |

| CSMA/CA | Carrier Sense Multiple Access / Collision Avoidance  |

| CSMA/CD | Carrier Sense Multiple Access / Collision Detection  |

| CSMA/CP | Carrier Sense Multiple Access / Collision Prevention |

| CTC     | Convolutional Turbo Code                             |

| DAC     | Digital-to-Analog Converter                          |

| DAG     | Design Assurance Guidelines                          |

| DAK     | Device Access Key                                    |

| DC      | Direct Current                                       |

| DER     | Distributed Energy Resources                         |

| DFT     | Discrete Fourier Transform                           |

| DLL     | Data Link Layer                                      |

| DNO     | Distribution Network Operator                        |

| DPD     | Duplicate Packet Detection                           |

| DS      | Data Service                                         |

|         |                                                      |

| DSP  | Digital Signal Processing                       |

|------|-------------------------------------------------|

| EAP  | Extensible Authentication Protocol              |

| EDS  | Ethernet Data Service                           |

| EMC  | Electromagnetic Compatibility                   |

| FC   | Frame Control                                   |

| FDM  | Frequency Division Multiplexing                 |

| FEC  | Forward Error Correction                        |

| FFT  | Fast Fourier Transform                          |

| FO   | Fiber Optic                                     |

| FOCA | Swiss Federal Office of Civil Aviation          |

| FPGA | Field Programmable Gate Array                   |

| GB   | Gateway Bridge                                  |

| GMA  | Grid Monitoring and Automation                  |

| GPS  | Global Positioning System                       |

| HD   | Hamming Distance                                |

| HIL  | Hardware-in-the-Loop                            |

| HIRF | High Intensity Radiated Fields                  |

| HSLU | Lucerne University of Applied Sciences and Arts |

| HW   | Hardware                                        |

| IFFT | Inverse Fast Fourier Transform                  |

| IFS  | Inter-Frame Spacing                             |

| ILA  | Integrated Logic Analyzer                       |

| IP   | Internet Protocol                               |

| LAN  | Local Area Network                              |

| LDP  | Line Differential Protection                    |

| LLC  | Logical Link Control                            |

| LNA  | Low Noise Amplifier                             |

| LUT  | Lookup-Table                                    |

| LV   | Low Voltage                                     |

| MAC  | Medium Access Control                           |

| MBD  | Model Based Design                              |

| MCS  | Modulation and Coding Scheme                    |

| MPDU | MAC protocol data unit                          |

| MSDU | MAC Service Data Unit                           |

| MTC  | Mission- and Time-Critical                      |

| MV   | Medium Voltage                                  |

| NMEA | National Marine Electronics Association         |

| NMK   | Network Management Key                         |

|-------|------------------------------------------------|

| OFDM  | Orthogonal Frequency Division Multiplexing     |

| OSI   | Open Systems Interconnection (Model)           |

| PB    | Physical Blocks                                |

| PCF   | Point Coordination Function                    |

| PCS   | Protection Communication Service               |

| PDN   | Power Distribution Network                     |

| PHY   | Physical Layer                                 |

| PL    | Programmable Logic                             |

| PLC   | Power Line Communication                       |

| PLS   | Physical Layer Security                        |

| PLUS  | Power Line data bUS                            |

| PMU   | Phasor Measurement Unit                        |

| PPDU  | PHY Protocol Data Unit                         |

| PPS   | Pulse Per Second                               |

| PS    | Primary Substation                             |

| PS    | Processing System                              |

| PSD   | Power Spectral Density                         |

| PUD   | Probability of occurrence of Undetected errors |

| QAM   | Quadrature Amplitude Modulation                |

| QPSK  | Quadrature Phase-Shift Keying                  |

| R2MDC | Radix-2 Multi-path Delay Commutator            |

| RAM   | Random-Access Memory                           |

| SFOE  | Swiss Federal Office of Energy                 |

| SISO  | Soft Input / Soft Output                       |

| SNMP  | Simple Network Management Protocol             |

| SNR   | Signal to Noise Ratio                          |

| SoC   | System-on-Chip                                 |

| SQNR  | Signal-to-Quantization-Noise Ratio             |

| SS    | Secondary Substation                           |

| TCP   | Transmission Control Protocol                  |

| TDMA  | Time Division Multiple Access                  |

| TEK   | Temporary Encryption Key                       |

| TRL   | Technology Readiness Level                     |

| UKE   | Unicast Key Exchange                           |

| V&V   | Verification and Validation                    |

| VGA   | Variable Gain Amplifier                        |

# VHDLVery High Speed Integrated Circuit Hardware Description LanguageWANWide Area Network

# 1 Introduction

#### 1.1 Overview

Worldwide, increasing pressure is being placed on the electric grids and in particular the Medium Voltage (MV) grids due to the steadily increasing introduction of Distributed Energy Resources (DER). The highly time-dynamic character of such power fed into the grid by a vast amount of spatially distributed sources combined with the decreasing ratio of stabilizing rotational mass leads to substantial challenges for the future grids to keep them robust enough for the requirements and expectations of the consumers. Grids must be able to accommodate new energy flow patterns in a considerably more dynamic environment.

Therefore, protection and automation systems are quickly gaining importance not only for the transmission grid but increasingly at the distribution grid level for the asset management programs of Distribution Network Operators (DNOs). This leads to the need not only for increasing the monitoring of the grid, but also to actively detect and mitigate the influence of potential faults in the grid. This requires critical applications such as voltage/congestion control and fault detection/location.

Phasor Measurement Units (PMU) measuring synchrophasors and Line Differential Protection (LDP) provide examples of such critical applications. They offer promising approaches for such high precision grid monitoring and automation. However, the communication requirements of such applications (high availability, low latency) provide a significant challenge to the communication infrastructure. Currently, there is no clear vision in the market on the exact communication technologies and network topologies which could fulfill these requirements. In any case there is a risk that such applications – which are well installed in the transmission grid today - in the distribution grid might lead to unacceptable cost figures which might prevent or in the best case delay the acceptance of such applications by DNO customers.

Such applications call for a larger amount of control and automation technology, but requiring at the same time cost-effectiveness in order to be bearable for the customers. For example, due to the pressure induced by the highly dynamic generation of renewables, it is no longer enough to use local measurements (V, I phasors and P,Q values) within each Secondary Substation (SS) for automation and protection, but more advanced monitoring and protection applications which require the exchange of measurements data between SSs are required. Distributed measurements between SSs will also be adding value by allowing the application of synchrophasors to the distribution level, helping to achieve efficient control of bidirectional power flows due to the massive integration of renewable energy systems.

These types of functionalities present a real challenge as the complete chain is involved, from the sensors, protection relays and various electronic devices integrated in the SS cubicle to the communication infrastructure to exchange the data between the SSs. Such communication infrastructure has to fulfil very high requirements regarding availability and latency, as will be described later on, and can therefore be considered as a Mission- and Time-Critical (MTC) communications infrastructure.

Considering the state-of-the-art in the communication infrastructure, there has already been a substantial change, as not long ago the communication equipment installed in these installations communicated through serial protocols with dispatch centers, due to the fact that the communication requirements were not very high in the electrical sector. However, still today there are only very few rollouts in which communications between SSs is provided.

Due to the large amount of SSs installed at the distribution level (ca. 4 Mio in Europe), the cost effectiveness of such applications including the communications system plays a critical role. Whereas Primary Substations (PS) at the transmission level are typically in an order of tens or few hundred, SSs are in an order of thousands or even tens of thousands for large utilities. A typical rule-of-thumb for DNOs is that the cost of equipment protecting the infrastructure should be less than 10% of the cost of the infrastructure to be protected. This further motivates a cost reduction of the protection equipment at the distribution level compared to the transport level.

Today's communication technologies do not completely fulfil the communication requirements for the above described applications with costs which are tolerable for a wide deployment in the distribution grid:

- Cellular networks (2G/3G/4G): latency too high, availability dependent upon the network operator and on the network load of other users

- Fiber Optic (FO) networks: fulfils the communication requirements but a full FO infrastructure is not bearable due to its significantly high costs

- MV Broadband Power Line Communications (MV-BPL): today's commercial technology does not support the reliability and latency requirements.

New solutions for the communication are therefore required, for fulfilling both the functional and the cost requirements.

### 1.2 Medium Voltage Broadband Power Line Communications

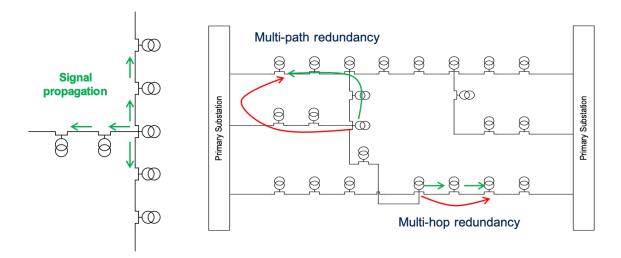

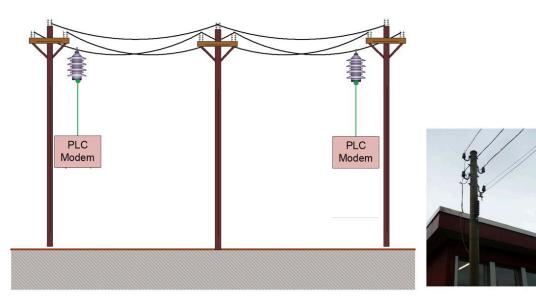

In this chapter an overview of the specific characteristics of a MV-BPL network will be provided which is partially necessary in order to understand the time-synchronization concepts presented later in this document. The MV distribution grid (i.e. 1 - 36 kV) comprises mainly underground cables, overhead lines and related infrastructure, including SSs. The MV grid mainly differs from the Low Voltage (LV) access and indoor grid in terms of the physical topology, cable/wire types and link distances. A broad range of SSs can be found depending upon the area (urban, suburban or rural) and consumption levels. Big utilities may operate hundreds of thousands of SSs. Such a heterogeneous set of SSs, however, presents a fundamental common infrastructure: MV lines which interconnect SSs among themselves and to PSs. The underlying topology of this interconnection can be considered as a meshed ring topology in which a certain amount of redundancy is provided between SSs and PSs. Links between SSs are usually very heterogeneous with several different cable types as well as a combination of overhead lines and underground cables being found in a single geographical area. While underground cables represent point-to-point links with relatively stable loads and impedances, overhead MV lines, on the contrary, may present taps in a tree-like topology.

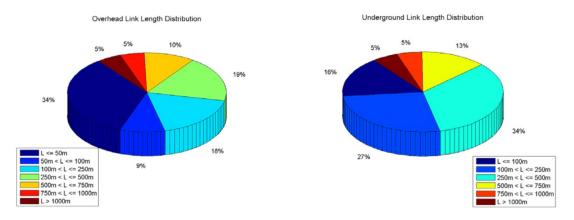

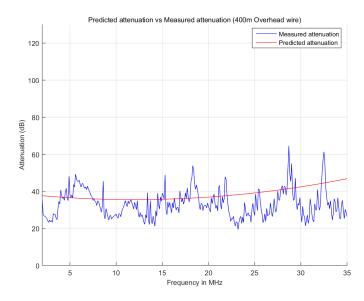

One typical misconception regarding the use of BPL in MV grids is that link distances are too long to support any reliable communications. Attenuation is a very important factor and will increase with distance and frequency, and as a consequence, longer MV links have to use frequencies in lower bands to guarantee a minimum performance. While it is true that BPL cannot achieve 100% coverage of all links in a typical MV grid (especially in rural areas), measurements have shown that raw data rates of several 10's of Mbps are possible for links up to 500 m. A general rule-of-thumb is that both older paper insulated lead covered and newer polyethylene insulated cables will support sufficient throughput on cables lengths up to 450 and 900 m, respectively. Measurements have been performed on overhead wires in which it was determined that reliable communications can be supported on links up to at least 2 km. A typical distribution of MV overhead wire and underground cable lengths is shown below in Figure 3. Analysis of actual MV grids in Spain and Switzerland have shown that MV-BPL can therefore cover 90%-95% of the overall grid.

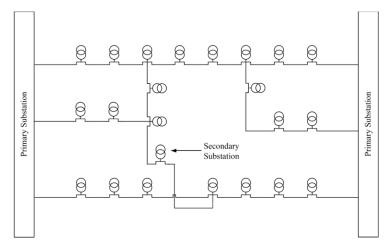

As previously mentioned, the topology of a MV grid can be described as a meshed ring topology in which SSs may have redundant paths to a single or multiple PSs (see Figure 1). This means that SSs will have anywhere from one MV feeder (endpoint) to several feeders per station. For the case of multiple feeders, individual phases (3-phase system) are connected across a common bus bar. Feeder lines are switched within the electrical grid such that a connected tree structure without loops is achieved. Load management and fault isolation can lead to manual or automated switching being performed in the grid. In order to achieve independence from the underlying electrical grid topology, but also to provide increased reliability through redundancy (redundant paths) coupling is generally performed on the feeder side of the switch (opposite the bus bar). This ensures that the logical BPL network topology remains independent of the MV grid's current switched state.

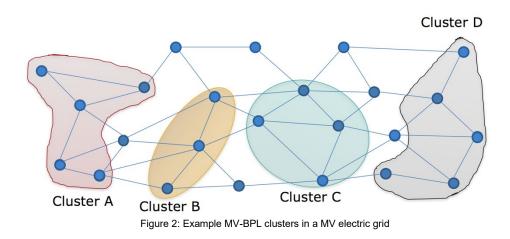

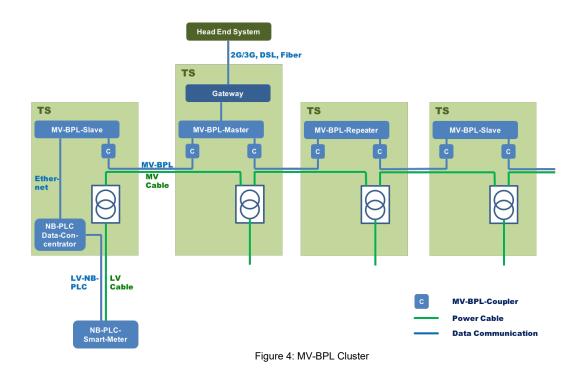

A critical aspect in the large-scale deployment and thereby the scalability of a MV-BPL network is defining a set of suitable guidelines for the cluster planning. In order to provide a scalable solution which can provide BPL coverage of a large MV grid, the network is typically divided into several clusters. As in cellular wireless networks, the communication nodes in a large-scale BPL network must be allocated to different clusters and channels must be assigned to these clusters. Each cluster consists of one master node which connects the cell to the backbone infrastructure, one or more repeaters used for extending the coverage and one or more slaves. Application endpoints may be attached to any BPL node within the network and the BPL network acts as a layer 2 switched Ethernet network. The master is the central node that controls and assigns resources to all the nodes in the network.

All nodes within a single cluster must be configured to operate on the same channel. As there is no BPL technology available which supports dynamic channel allocation between clusters, channels must be manually allocated to clusters such that neighboring clusters operating on the same channel will not interfere with each other. Interference between neighboring clusters can be avoided by using a guard distance between the clusters which are using the same channels. Because of this guard distance, gaps or regions which cannot be covered by BPL may exist in the network (see example in Figure 2). These regions must then be covered by alternative technologies. To increase the amount of channel reuse within the network and minimize the gaps in coverage, multiple channels are used similar to the channel assignment problem known from mobile wireless networks.

Figure 1: Example of a ringed-mesh topology

Figure 3: Typical distribution of MV overhead wire (left) and MV underground cable link lengths for urban/sub-urban environments

### 1.3 Challenge

The motivation behind this project is the development of a new Grid Monitoring & Automation (GMA) solution which takes advantage of the full potential of MV-BPL for enabling MTC-GMA applications in the MV grid. The main driver behind this idea is to provide increased observability and stability to the grid using functionalities previously only used in transmission grids, but for a much lower price that will enable a broad rollout of these functionalities into the distribution grid.

The state-of-the-art in MV automation developments over the last years has provided visibility to the MV grid all over the network, especially with the availability of accurate grid measurements. This visibility allows centralized advanced automatic functions to be realized. The future vision is to provide a synchronized exchange of GMA data from the installed equipment between neighboring SSs which would provide much more value through optimized distributed monitoring, protection and automation functions (PMU, LDP).

The idea is to achieve this through a further development of the MV-BPL technology by enabling MTCfunctionality with time synchronization, higher availability and low-latencies permitting the PMU and LDP functionality. The basis for this development is the Power Line data bUS (PLUS) BPL technology which has been developed at the Lucerne University of Applied Sciences and Arts (HSLU). The major advantage being the fact that HSLU has complete control over all aspects of the technology allowing the necessary features and optimizations for such vertical applications to be realized.

In order to achieve the overall goal, the neighboring SSs would be interconnected through this lowlatency and high-availability MV-BPL network. The application devices could thus exchange synchronized phasor measurements creating a synchronized monitoring area. This would allow the instantaneous exchange of data and online system analysis of the area to be performed. Furthermore, the LDP application would provide automatic fault detection and mitigation thereby protecting the DNO's important infrastructure and providing higher availability of the electric grid.

The major value of the proposed communication solution with MV-BPL is the low cost. For such functionality – today implemented on the transmission grid level only - a very expensive fiber optic communication would have been required. With the MTC-MV-BPL solution this could be avoided, as the MV lines between the SSs are re-used as the communications medium.

This would lead to a next step in the implementation of MV-BPL clusters. A MV-BPL cluster consists of a number of SSs which are connected together forming a MV-BPL network (see Figure 4 as an example). Within a cluster a single MV-BPL modern will simultaneously act as the network master and serve as a gateway between the MV-BPL network and the Wide Area Network (WAN). The MV-BPL moderns within other SSs serve as repeaters or as slaves. The potential for establishing multi-hop communications allows a single MV-BPL cluster to cover a large geographic area. Within this area only a single (typically expensive) connection to the WAN is required rather than a single connection per SS. This reduction in the number of expensive WAN connections provides a further cost advantage for MV-BPL.

Up to now such MV-BPL clusters have been implemented for Automated Metering Infrastructure (AMI). For this use-case, smart meter data is collected by the data concentrator using narrowband PLC technology for the connection between the SS and the meter. The data from the data concentrators in each SS is then further aggregated within the MV-BPL network and transmitted to the head end system through the gateway at the MV-BPL master. The largest current deployment of this solution is in Spain with the utility Iberdrola [1]. However, the network performance requirements for the AMI application are rather relaxed compared to the proposed GMA applications.

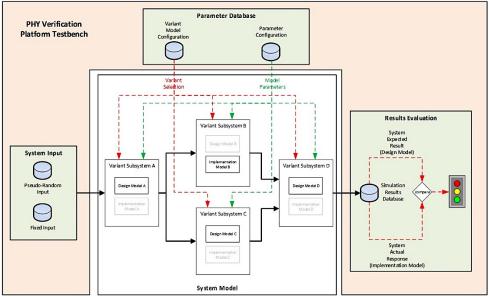

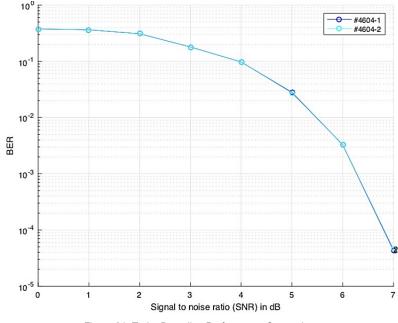

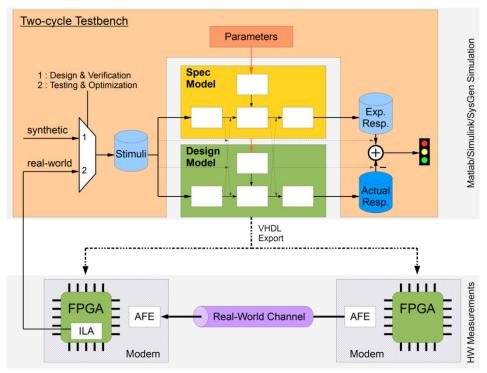

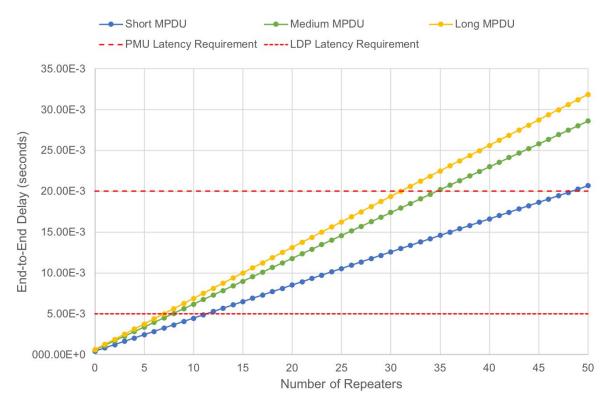

Therein lies the challenge. A comparison of the addressed applications is shown below in Table 1. The most critical requirements are highlighted in red. The target of this project is to address the strict latency requirements which are highest for the LDP application (<5 ms). Fulfilling the low latency requirements of GMA applications poses a significant challenge for the communication technology, since a very powerful Modulation and Coding Scheme (MCS) is required for MV-BPL to provide robust communications over the unreliable communications medium. The use of such complex MCS has led to relatively high processing times at both the transmitter and receiver which makes achieving this latency requirement a challenge. Therefore, a detailed research-oriented investigation including simulations within a Model Based Design (MBD) approach was required to optimize the MCS towards minimizing latency. This project has covered a research-based exploration of the optimum schemes and protocols based on the vast experience at HSLU regarding PLC channels, transmission schemes, protocols, etc. A concept and design for an adaptation of the existing schemes and protocols has been developed, mainly based on simulation results tested and optimized on a verification platform.

| Requirement                                   | АМІ                                                                        | AMI LDP Synchro                                |                                                                     |

|-----------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------|

| Transmission Frequency                        | Once per day                                                               | Constant transmission<br>of measurement values | Constant transmission<br>of measurement values                      |

| Bandwidth                                     | 100 kbps per SS                                                            | 10 kbps per SS                                 | 65 kbps per SS                                                      |

| Latency                                       | Not relevant<br>(time-intolerant)                                          | < 5 ms                                         | < 20 ms                                                             |

| Bit error rate                                | No specific requirement                                                    | 10 <sup>-6</sup> or better                     | No specific requirement                                             |

| Availability                                  | Network must be<br>available for transmission<br>of data only once per day | 99.99% availability                            | High-availability if real-<br>time state estimation is<br>performed |

| Data Integrity                                | No specific<br>requirements <sup>1</sup>                                   | 100% data integrity <sup>2</sup>               | 100% data integrity <sup>2</sup>                                    |

| Time-synchronization<br>Accuracy <sup>3</sup> | Not required                                                               | ±100µs                                         | ± 3.1µs                                                             |

Table 1: MV-BPL performance requirements for smart grid applications

<sup>&</sup>lt;sup>1</sup> Undetected errors will not lead to a large impact on operations.

$<sup>^{2}</sup>$  The typical definition is a probability of undetected error of 10  $^{9}$  per operational hour.

<sup>&</sup>lt;sup>3</sup> We assume here that time-synchronization is provided by the network so it is a requirement of the network.

# 2 Goal of Project

### 2.1 Main Goal

An investigation will be carried out how Broadband Power Line Communications can be used in the distribution grid which fulfills the communication requirements of Phasor Measurement Units (PMU). The goal is to provide a low-cost communication interface in order to open the door for the more widespread use of PMUs in the distribution network.

### 2.2 Report Outline

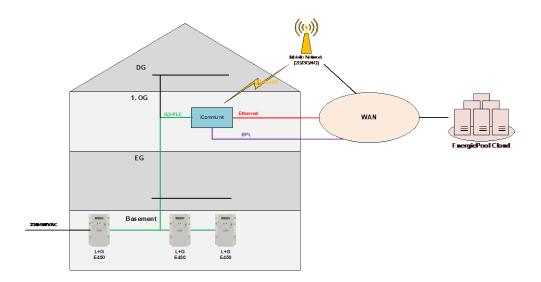

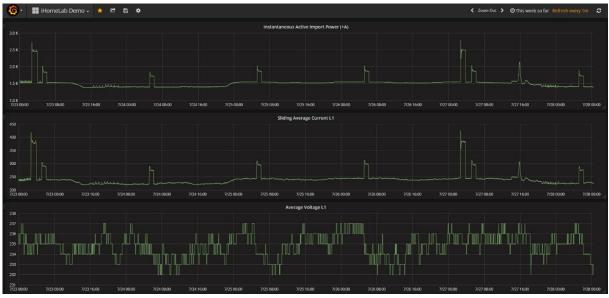

The basis for the development of the MTC-MV-BPL solution is the Power Line data bUS (PLUS) PLC technology developed by the Lucerne University of Applied Sciences and Arts (HSLU). The general architecture and requirements for the MV-BPL technology have been previously described in Chapter 1.2 and Chapter 1.3, respectively. A description of the PLUS technology is provided in Chapter 3. The main application of the area prior to this project has been for avionics systems. The technology has to a certain extent been optimized for this environment (known as PLUS-Avionics). Therefore, the first step in the project was to analyse the technology compared to the PMU application requirements and determine the necessary adaptations and optimizations. This has resulted in a variant of the PLUS technology known as PLUS-Smart Grid. The motivation for the necessary design changes in moving from PLUS-Avionics to PLUS-Smart Grid are described in Chapter 4. Chapters 5 and 6 then describe the adaptations and optimizations in more detail. For technologies for MTC applications it is not only important to consider the high-level design of the technology, but also the processes behind the design and development of the technology. Within this project an optimization to the existing development process of PLUS has also been developed which is described in Chapter 7. Furthermore, security plays a critical role in MTC communications. A security analysis of the MTC-MV-BPL technology has also been performed and is described in Chapter 8. The identified adaptations and optimizations for the PLUS-Smart Grid technology have all been implemented on a set of prototypes. These prototypes are described in Chapter 9. Functional and performance testing has then been performed within HSLU's Smart Grid CommTech Testbed Laboratory which has been developed in conjunction with BKW. In addition to the PMU application requirements, the developed prototypes have been tested for the AMI application against existing prototypes of the iCommUnit product provided by Energie Pool AG. Energie Pool has partially financed the work in this project in order to compare the newly developed MTC-MV-BPL solution against the existing G3-PLC technology in the iCommUnit prototypes. The test setup and results are provided in Chapter 10. Finally, conclusions and next steps for the development of the technology are presented in Chapter 11.

# 3 Power Line data bUS (PLUS) Technology

### 3.1 Introduction to Power Line Communications (PLC)

PLC is a wired communication technology that is able to use a Power Distribution Network (PDN) for data transmission by superimposing a modulated high frequency carrier signal over the standard power signal. The PLC signal is modulated completely independent of the underlying power signal, i.e. will function over any DC, AC or even non-energized systems. PLC combines the advantages of wireline communications with the use of an existing (non-dedicated) wiring network. The specific advantage of PLC comes due to the fact that it has been specifically designed for communications over wiring channels that have not been designed for high-speed data communications, e.g. over unshielded wires in noisy environments. Because of its robustness, the PLC technology may be employed to reliably communicate over any shielded or unshielded wired networks that are normally used for low frequency applications such as power lines, telephone lines (twisted pair copper) or low data rate signaling/control lines.

Similar to wireless communications, the term PLC refers to a broad range of diverse communication protocols. Furthermore, as is also the case for wireless communications, certain protocols may be better suited for avionics applications and one should be careful in drawing conclusions based on the analysis of commercial protocols developed for the consumer electronics market. PLC technology is typically divided into two different categories depending upon the band used by the communications signal.

- Narrowband PLC frequencies below 500 kHz can provide maximum data rates up to several 100's of kbps, however practical and regulatory limitations lead to a more typical achievable data rate of several 10's of kbps.

- Broadband PLC operates somewhere in the frequency range from 2-80 MHz. Commercial PLC technologies can provide maximum data rates up to 500 Mbps.

What really defines PLC as a technology is the robustness of the communication protocols to the harsh communication channel which exists in Power Distribution Networks (PDN). This mainly involves a multi-carrier transmission scheme in the form of Orthogonal Frequency Division Multiplexing (OFDM) which optimizes spectral efficiency in the presence of a frequency selective channel. Other important features provided by PLC are strong Forward Error Correction (FEC) techniques (e.g. turbo-convolution or low-density parity check codes) to combat impulsive noise. It is these robust protocols that allow high data rates to be achieved over wiring networks not normally supporting data communications such as can be found in PDNs.

### 3.2 Challenges of PLC

The use of PLC does not come without its challenges. PDNs have been optimized for the distribution of a very low-frequency power signal and are rather unsuitable for high-speed data communications.

The following main factors differentiate the wiring of a PDN from the wiring typically found in data networks

- PDN wiring is typically unshielded.

- PDN wiring will not consist of a twisted-pair but will usually either consist of a single-wire with return over a common chassis or a group of wires routed in parallel. This often leads to a highly asymmetric transmission medium.

- The PDN topology is often tree-like and contains a number of branches or other points at which impedance discontinuities will occur with impedances varying between a few ohms to a few kiloohms.

- The impedance of loads attached to the PDN is optimized for the maximum power transfer of the power signal and is rather arbitrary for higher frequencies.

- Power conversion and other active power elements within loads will generate static and transient noise which will be conducted or even coupled from external sources onto the PDN.

These characteristics lead to a less than ideal communications channel.

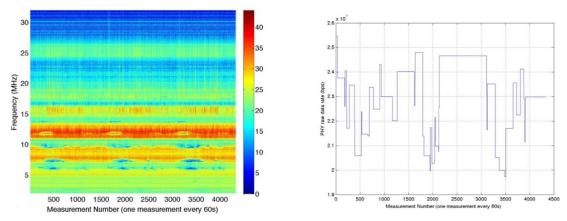

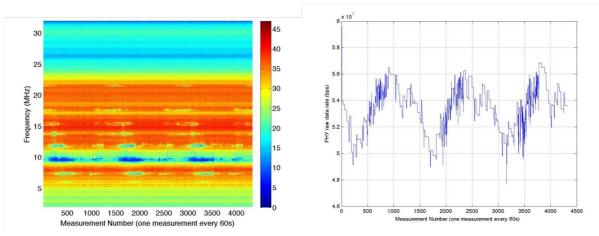

- Impedance mismatches will exist at the loads, branching points and other connection points throughout the PDN.

- Each impedance discontinuity will lead to a partial transmission and partial reflection of the PLC signal. At branches the signal power will be split with partial transmission of signal "echoes" down each of the branches. At the receiver these different echoes and reflections will combine leading to highly frequency selective attenuation. Several "notches" or narrow bands which suffer from higher attenuation than adjacent bands will be present. This effect is commonly referred to as multipath fading. As the paths and load impedances between any two transmitters and receivers will vary, so too will the transmission channels vary. This means that the communications channel has a strong dependence upon the location of the transmitter and receiver. Figure 5 shows a typical PLC communications channel. This was taken from a channel measurement on a 400 m section of MV overhead line. The highly frequency selective attenuation with a few deep "notches" is apparent. It is also apparent that the mean attenuation increases versus frequency which is mainly due to the skin effect and dielectric losses from the insulating material.

Figure 5: Example PLC channel attenuation for MV overhead line

The PLC communications channel will therefore exhibit the following characteristics

- High transmission signal attenuation (up to ca. 80 dB)

- Frequency selective channel (a channel in which the attenuation varies versus frequency)

- Transient or "bursty" noises exist on the channel

- High power narrowband interference, e.g. from broadcast radio carriers

- Interference from external systems (e.g. adjacent channels) which may be coupled onto the power line due to the fact that it is typically unshielded

- Impedance conditions on the transmission channel may vary versus time, e.g. load impedance changes due to different states of attached application equipment.

It is a common misconception that PLC cannot communicate given these channel characteristics. On the contrary the PLC technology - especially the digital signal processing in the physical layer - has been optimized for over 20 years now to provide reliable communications under these harsh channel conditions. Where traditional data bus protocols would fail, PLC is still able to provide reliable communications.

It is a well-accepted fact that the noise on a power line does not have properties of a "white" Gaussian noise. Typically, three general classes of noise can be expected:

- Colored background noise with a higher Power Spectral Density (PSD) at lower frequencies

- Narrowband background noises which may result from external sources (e.g. broadcast radio) or system internal sources (e.g. application device clock signal)

- Impulsive noise which may be generated from multiple sources at the loads including on/off switching behavior, switched power supplies, etc.

Furthermore, the lack of a shield or twisting of the power cables means that the potential isolation from external effects which may be electro-magnetically coupled onto the power line is reduced. External sources of noise can be other aircraft systems operating within the same (or a nearby) wiring harness, High Intensity Radiated Fields (HIRF) from broadcast radio, low-frequency voltage spikes, lightning, etc.

The main factor influencing the performance of any communication system is the Signal-to-Noise-Ratio (SNR) present at the receiver. Therefore, even in environments with high channel attenuation or high noise, an increase in the transmission signal power could still provide a sufficient SNR. However, within many environments in which PLC is used, the emissions of all devices within the PLC signal frequency range is strictly regulated through Electromagnetic Compatibility (EMC) limits. Even though PLC provides intentional emissions within this band, from the EMC point-of-view it must be categorized as unintentional emissions or noise. These limits mean that the transmission PSD of the PLC signal must be limited in order to be in compliance with the limit for the relevant environmental category.

The fact that the PLC signal propagates over a fixed wiring network means that the channel will exhibit a certain amount of determinism. Time-varying behavior in an installed PLC system typically only result from the time-varying impedances of loads or switching within the network. Proper filter and coupler design can provide a solution which reduces the influence of application device impedance changes on the PLC channel, thereby providing less time-varying behavior. Wireless communication is often considered alongside PLC as a communications technology since it provides many of the same advantages. However, the dynamic propagation environment of a wireless signal poses a significant challenge for the use of the technology in safety-critical applications due to the highly random and

time-varying nature of the wireless channel. The determinism provided by PLC is considered to be one of the main advantages for the use of PLC over wireless technology. Table 2 shows a comparison of PLC to other communications technologies.

|                                             | PLC                                                                                                  | Traditional Data Buses                                                                                               | Wireless                                                                               |

|---------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Transmission<br>Medium                      | Electrical power<br>distribution network                                                             | Dedicated wiring                                                                                                     | Free space                                                                             |

| Harness<br>Requirements                     | <ul> <li>No data network<br/>harness</li> <li>No change to power<br/>network requirements</li> </ul> | <ul> <li>Strict requirements for<br/>data network harness</li> <li>Separation of<br/>data/power harnesses</li> </ul> | <ul><li>No data network<br/>harness</li><li>Power network still<br/>required</li></ul> |

| Communications<br>Channel                   | Mainly deterministic                                                                                 | Highly deterministic                                                                                                 | Highly variable                                                                        |

| Environmental<br>Susceptibility             | Moderate                                                                                             | Low                                                                                                                  | Very high                                                                              |

| Communications<br>Channel<br>Susceptibility | Moderate <sup>1</sup>                                                                                | Low <sup>2</sup>                                                                                                     | Very high                                                                              |

| Security                                    | Communications medium inaccessible to attackers                                                      | Communications medium inaccessible to attackers                                                                      | High risk of availability,<br>integrity and<br>confidentiality attacks                 |

| Flexibility                                 | Moderate                                                                                             | Low                                                                                                                  | High                                                                                   |

Table 2: PLC vs. Traditional Data Buses vs. Wireless (1) Communications protocols designed to tolerate high levels of noise, (2) Susceptibility achieved through proper wiring harness construction and separation.

### 3.3 Power Line data bUS (PLUS)

The potential application of PLC for Mission-and-Time Critical (MTC) applications is not new. Previous work by HSLU for avionics applications performed within the EU FP7 TAUPE project has validated the technology up to a Technology Readiness Level (TRL) of 4 [2]. Nevertheless, previous investigations were based on the use of commercial PLC technology and certain deficiencies with that technology had been identified [3]. Unfortunately, the relatively small market segment provided by many MTC applications results in a general lack of support for any necessary adaptations to the commercial technology by the technology suppliers<sup>4</sup>. A "black-box" verification of this technology without support from the technology suppliers would be extremely challenging.

Based on the need for a PLC technology to support the requirements of MTC applications in niche market areas, the development of a dedicated PLC solution was started at the Lucerne University of Applied Sciences and Arts (HSLU) in 2012. The main design goals for the PLC protocol were to maximize reliability, reduce latency and to provide deterministic behavior. These goals are different from commercial technology which includes much dynamic behavior in order to support plug-and-play and high bandwidth applications. The HSLU PLC solution (Power Line data bUS - PLUS) not only targets a communications protocol which meets the necessary functional and performance requirements, but also provides design assurance as is required for MTC applications.

PLUS is the only PLC technology which has been developed specifically for use in MTC applications. PLUS has been designed around:

• Proven standard from other industries for the physical layer (IEEE 1901)

<sup>&</sup>lt;sup>4</sup> Based on actual feedback from commercial PLC technology suppliers sales quantities of 500'000-1'000'000 are required for them to support new application areas.

- Proven avionics standard for bus arbitration (ARINC 629)

- Custom optimizations and additional protocol layers

- Using available bandwidth to optimize data availability and integrity

The following lists some of the differentiating factors of the PLUS protocol compared to other commercial PLC solutions:

- Bus arbitration is based on a deterministic protocol with no single point-of-failure

- Synchronization for signal decoding (due to asynchronous clocks) is done in a distributed manner, i.e. no central bus/clock master is required

- Error detection is based on optimized techniques from the avionics industry

- Support for multiple independent communications channels through a Frequency Division Multiplexing (FDM) feature

- Robust modes have been optimized for low-latency; robust transport of short messages (< 20 bytes)</li>

- Multiple services can be multiplexed onto a single PLC bus while still providing deterministic behaviour

- Connections are stateless so that the protocol behavior remains static and provides more determinism

- Optimizations have been made to improve susceptibility especially to impulsive and strong narrowband interference, e.g. HIRF

The specification for PLUS Avionics is shown in Table 3.

| PLUS Specification                          |                                                                                                                               |                                                                 |                      |                     |                       |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------|---------------------|-----------------------|--|

| Physical Layer<br>Signal                    | Multi-channel Orthogonal Frequency Division Multiplexing (OFDM) with 2048-point FFT                                           |                                                                 |                      |                     |                       |  |

| Modulation                                  | BPSK, QPSK, 8-QAM, 16-QAM                                                                                                     |                                                                 |                      |                     |                       |  |

| Frequency Range                             | 2-42 MHz                                                                                                                      |                                                                 |                      |                     |                       |  |

| Channel Modes                               | Mode A                                                                                                                        | Mode B                                                          | Mode C               | Mode D              | Mode E                |  |

| Channel Bandwidth                           | 40 MHz                                                                                                                        | 30 MHz                                                          | 20 MHz               | 10 MHz              | 5 MHz                 |  |

| Sub-carrier Spacing                         | 24.414 kHz                                                                                                                    | 16.276 kHz                                                      | 12.207 kHz           | 6.104 kHz           | 3.052 kHz             |  |

| OFDM Symbol<br>Duration                     | 40.96 µs                                                                                                                      | 61.44 µs                                                        | 81.92 µs             | 163.84 µs           | 327.68 µs             |  |

| Physical Data Rates                         | 20 Mbps –<br>142 Mbps                                                                                                         | 14 Mbps –<br>104 Mbps                                           | 10 Mbps –<br>71 Mbps | 5 Mbps –<br>35 Mbps | 2.5 Mbps –<br>17 Mbps |  |

| Forward Error<br>Correction                 | Convolutional                                                                                                                 | Convolutional Turbo Coding with code rates 1/2, 16/21 and 16/18 |                      |                     |                       |  |

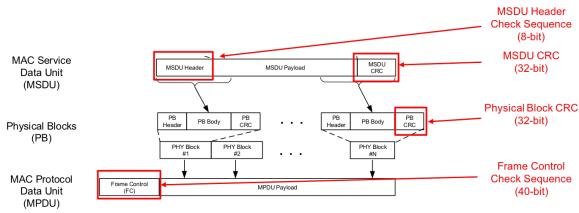

| Error Detection                             | Multi-level Cyclic Redundancy Check (CRC)<br>CRC-40, CRC-32, CRC-8                                                            |                                                                 |                      |                     |                       |  |

| Bus arbitration                             | ARINC-629 B                                                                                                                   | ARINC-629 Basic Protocol with bus quiet time optimization       |                      |                     |                       |  |

| Network<br>Architecture                     | Peer-to-peer without central clock master                                                                                     |                                                                 |                      |                     |                       |  |

| Network<br>Setup/Management                 | <ul> <li>Zero network setup time</li> <li>No network management traffic</li> </ul>                                            |                                                                 |                      |                     |                       |  |

| Data services                               | <ul> <li>Gateway functionality for CAN bus, Ethemet / IP</li> <li>Multiplexing of multiple data services supported</li> </ul> |                                                                 |                      |                     |                       |  |

| Supported power<br>distribution<br>networks | 28VDC, 115VAC, 230VAC, 270VDC                                                                                                 |                                                                 |                      |                     |                       |  |

Table 3: PLUS Avionics Specification

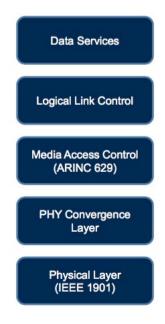

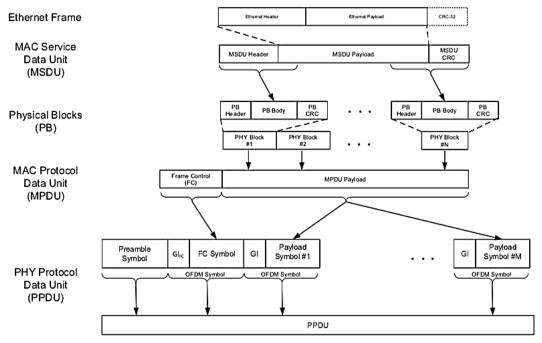

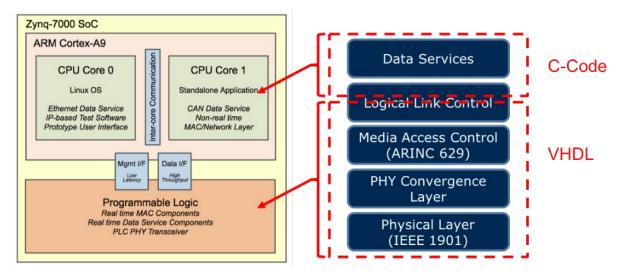

The PLUS Avionics protocol defines Layer 1 and Layer 2 according to the OSI network model. This is further segmented into 5 sub-layers as shown in Figure 6:

- 1. Physical Layer

- OFDM based physical layer

- Based on international IEEE 1901 OFDM standard

- 2. PHY Convergence Layer

- Adaptation of MAC frames to physical blocks

- 3. Media Access Control (MAC) Layer

- Monitoring of the bus state

- Scheduling of the transmission on the bus (core algorithm based on ARINC-629)

- 4. Logical Link Control (LLC)

- Flow control and multiplexing

- 5. Data Services

- Adaptation of one protocol to PLUS (gateway functionality)

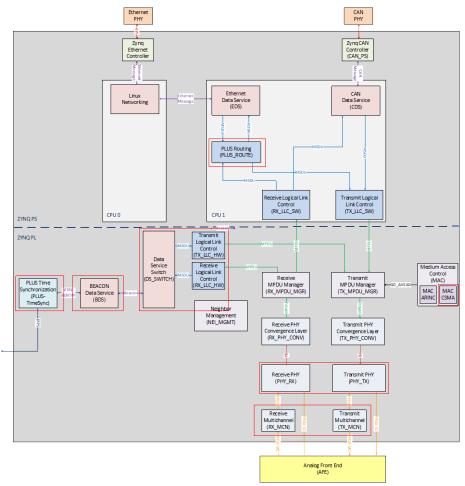

### 3.4 PLUS Modem Architecture

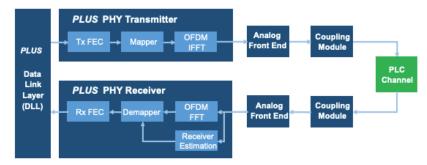

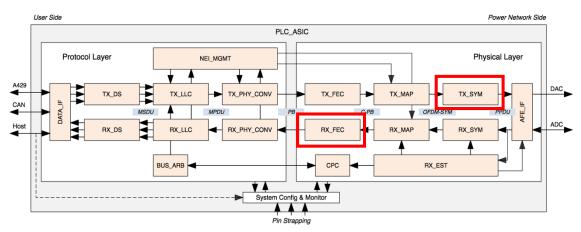

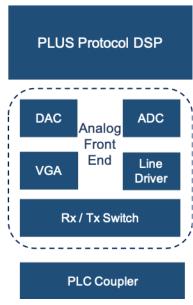

An overview of the architecture of a PLC modem is shown in Figure 7. The Digital Signal Processing (DSP) contains the logic implementing the PLC protocol including the implementation of the physical layer (PHY) and Data Link Layer (DLL). The PHY transmitter is responsible for converting the PLC MAC frame provided by the DLL into a PLC signal waveform suitable for transmission on the power line medium. The PHY receiver on the other hand decodes the PLC signal waveform into a MAC frame which is passed to the DLL. The Analog Front End (AFE) provides Digital-to-Analog, Analog-to-Digital and amplification functionality for the analogue signal. The coupler is responsible superimposing the high-power, low-frequency power signal with the low-power, high-frequency PLC signal.

Figure 7: PLUS Modem Architecture

Figure 6: PLUS Protocol Architecture

Two different principle coupling methods are available in PLC: capacitive and inductive coupling:

#### **Capacitive coupling**

- PLC signal is capacitively coupled to the power line.

- Generally, it provides better impedance stabilization when the impedance of the PLC channel is highly varying.

- Component dimensioning is crucial mainly for high voltage applications (> 400 V).

- The disadvantage is that a galvanic connection to the power line is required (although the PLC modem is typically galvanically isolated with a further transformer.

#### Inductive coupling

- PLC signal is inductively coupled to the power line.

- Galvanic connection to the power line may be avoided if necessary, however capacitive elements (with a galvanic connection) may still be required for filtering.

- Component dimensioning is crucial to ensure that the PLC signal does not saturate with high currents.

Figure 8: Capacitive Coupling Example

Figure 9: Inductive Coupling Example

Load management and fault isolation can lead to manual or automated switching being performed in the network. In order to achieve independence from the underlying electrical network topology, but also to provide increased reliability through redundancy (redundant paths) coupling is generally performed on the feeder side of the switch (opposite the bus bar). This ensures that the logical PLC network topology remains independent of the MV network's current switched state. Complete independence of the switch state, however, cannot be achieved as the coupler loss will be dependent upon the state of the switch due to fact the impedance seen by the coupler will change during switching. Inductive coupling will generally function better in a closed switch state (low-impedance) and capacitive coupling in an open switch state (high-impedance). The selection of a coupling method is influenced by the cable/wire type as well as the characteristics of the transformer and switch. However, coupler selection may also be influenced by practical limitations such as confined space, safety distance requirements or other installation constraints. Safety regulations will generally require that couplers be installed on non-energized lines.

#### 3.5 PLUS-TimeSync

Within a previous SFOE funded project the PLUS technology was extended in order to support highly accurate time synchronization over a PLUS network [4]. A time synchronization accuracy of  $\pm$  0.5  $\mu$ s over two-hops in a network could be achieved under wide-ranging test conditions. The Time

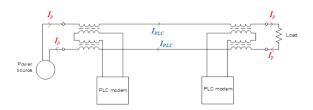

Synchronization Protocol for PLUS (PLUS-TimeSync), defines a solution for a highly accurate time synchronization between PMU application devices on top of a MV-BPL network. The developed BPL solution with time-synchronization will provide a cost-efficient alternative to existing PMU systems based on fiber optic communications and GPS-based time-synchronization. A system design has been defined allowing each BPL cell to not only synchronize all devices within the cell, but also synchronize to the absolute time outside of the cell.

The end-to-end synchronization has been divided into four different zones as is shown in Figure 10. This hierarchical architecture was selected in order to provide a scalable solution in which an optimized solution is provided for the specific technical characteristics of each zone. This architecture also takes into consideration the cellular nature of a larger BPL network in which each cell is controlled by a MV-BPL master modem. This also allows any loss of synchronization to error conditions to be partially contained within a single zone meaning that the impact will not have a direct impact on the complete system.

**Zone A**: Synchronization of the grand master clock at the BPL master with the absolute time. This synchronization takes into consideration providing not only a highly accurate solution, but also a solution that is robust against potential security attacks. For that a combination of different technologies are used allowing a sanity check to be made against the obtained time-synchronization and also providing a fallback solution should one of the synchronization sources be lost.

**Zone B**: Synchronization across the MV-BPL network. The MV-BPL master acts as the time synchronization grandmaster. In order to ensure a standardized BPL solution can be provided this network based synchronization was defined within the framework of the IEEE 1901 BPL standard. Although the standard does not directly allow for a synchronization with the required accuracy the necessary modifications were identified and defined. The required message exchange, however, makes use of management messages which are defined by IEEE 1901 using vendor specific extension fields.

**Zone C**: Synchronization within the BPL modem between the clocks for zone A and zone C. The synchronization in zone A and zone C is, in principle, running asynchronously. However, in order to provide very high accuracy these two clocks must be synchronized. The developed design takes into consideration the specifics of the target hardware platform which is the Xilinx Zynq System-on-chip.

**Zone D**: Synchronization to end devices using a standard one pulse per second (1PPS) interface. This provides the most accurate and simple means to synchronize to an end device. Along with the 1PPS signal the absolute time is output as a NMEA sentence. Therefore, the BPL modem always acts as the time master and the attached device is the time slave. This allows the developed solution to interface to existing application devices (even beyond that of the PMU application) without requiring modifications to the devices. This interface is very similar to the absolute time input interface used in Zone A.

Figure 10: PLUS-TimeSync System Architecture

# 4 PLUS Smart Grid Design

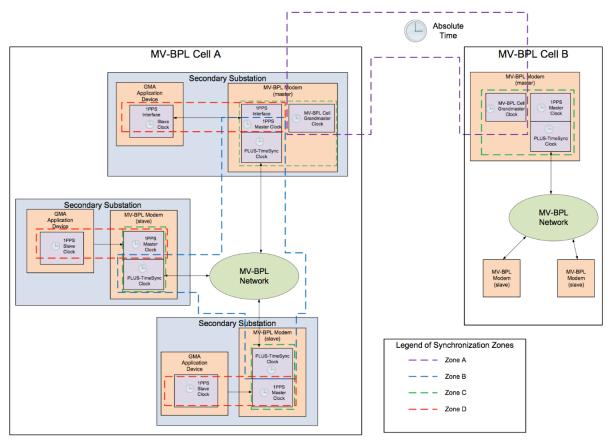

The main metric for determining the performance of any communications system is the SNR at the receiver. The SNR is dependent upon the transmission PSD, the attenuation in the transmission channel and the noise. Each of those characteristics may be both frequency- and time-variant. The communications channel capacity (rate at which information reliably transmitted over a communications channel) is a direct function of the SNR.

There are a number of performance requirements that an MTC data bus must fulfil. In general, these can be summarized by the five categories presented in Figure 11. The available channel capacity is the main factor for determining if these performance requirements can be met. However, this is presented as a multi-goal optimization problem. Optimizing one of these performance goals will lead to a negative influence on the other goals. Here are some examples:

- Increasing the power will improve the throughput and/or reliability, however it will reduce the EMC

- Using re-transmissions improves reliability, but it reduces the effective throughput and increases latency

- Increasing the number of nodes reduces the effective throughput for each node and increase the latency

- Increasing the throughput can be realized by using higher order modulations (more bits per sub-carrier), however these high order modulations are more prone to errors, i.e. have a low reliability.

Figure 11 captures this design trade-off. It also captures another area of communications system design, namely the deterministic quality of the performance. As previously mentioned, the SNR may be time-variant. This inherently leads to the fact that the performance may also being time-variant. In some application areas it is acceptable if, for example, the throughput reduces to almost zero for a brief time as long as it is very high in the average. For avionics applications this is not the case. Deterministic behavior is required. Achieving deterministic communications system behavior requires proper design consideration. This factor is also captured in Figure 11.

The grey area represents the commercial PLC technology. The design of that technology attempts to maximize throughput which comes at the cost of the other performance metrics. However, the technology is largely non-deterministic meaning that in the best case the throughput may be very high (e.g. several hundreds of Mbps). However, in the worst case the throughput will be very low or even zero. The technology is highly adaptable which inherently leads to dynamic behavior. The spontaneous performance at any point in time can vary within the grey area in this figure.

PLUS follows a different design approach. More weight is placed on maximizing reliability, reducing latency and achieving EMC compliance. In most scenarios it is also necessary to support larger network sizes. Achieving these optimization goals will inherently lead to an overall reduction in the achievable throughput. The solution will also provide deterministic behavior. This is shown in Figure 11 by the fact that the achievable performance area (red band) is much narrower than the grey area for the commercial technology.

Figure 11: PLUS Design Trade-off

# 5 Latency Optimization

### 5.1 Latency in Communications Systems

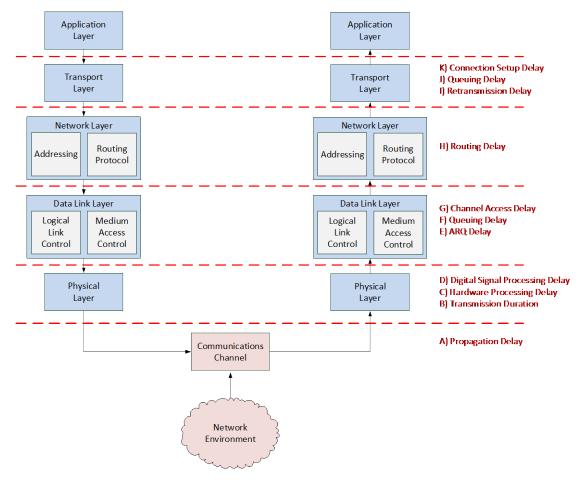

A communication system is portioned in different logic layers according to the OSI model (see Figure 12 and [5]). Latency within a communications network can be defined generically as the time it takes for a packet (or message) to get from the transmitter to the receiver. More specifically, when looking at the OSI model, it is the time it takes for a message to be sent from the application layer of the sender to the application layer of the receiver. This is due to the fact that the application layer is the highest layer responsible for generating and processing communications messages.

Latency can be introduced at each layer depending upon the communications protocol. The main sources of latency associated with each layer are shown in Figure 12 and described here:

- A. Propagation Delay: The amount of time it takes for the beginning of the communications signal to travel from the transmitter to the receiver. The propagation is a function of the physical distance and the transmission medium. For certain communications technologies like wireless and PLC it is important to not only consider the propagation delay of the direct signal, but also the propagation delay of the different "echoes" or paths other than the direct path which the communications signal traverses. This is due to the fact that the receiver may synchronize to and decode one of these echoes rather than the direct path signal.

- B. Transmission Duration: In most modern communications protocols the complete data frame must be available at the Data Link Layer (DLL) before it can be fully processed at the receiver. This means that each decoded bit from that frame must be buffered and the frame can only be passed to the upper layers once all bits are available. This leads to the fact that the duration of the overall communications signal must be also considered as part of any delay calculation. The duration can be considered as the time between the very beginning and the very end of the communications signal. This will also include any overhead within the signal which could include preambles, headers, etc.

- C. **Hardware Processing Delay**: Almost all modern communications systems will convert the analog communications signal into a digital signal for further Digital Signal Processing (DSP) by the physical layer (PHY). Furthermore, the signal is often times filtered and amplified within the analog domain. This leads to a non-zero delay from the time that the beginning of the analog communication signal reaches the hardware receiver to the time that the digital communications is input into the digital processor for further DSP.

- D. **Digital Signal Processing Delay**: The advanced DSP techniques used by modern communications systems means that the time required for the PHY receiver to completely decode all the bits associated with the data frame is non-zero. In other words the last bit from the data frame will not be decoded until a certain amount of time after the end of the communications signal. This difference between the end of the communications signal and the time that the PHY receiver is finished decoding the last bit within the data frame can be considered as the DSP delay.

- E. **ARQ Delay**: Typically Automated Repeat reQuest (ARQ) will be used at the DLL which is a means by which erroneous frames are re-transmitted in order to improve the reliability of delivery. The need for re-transmission is determined based on feedback from the receiver through the use of acknowledgement frames. Therefore, the use of ARQ will lead to a delay in two cases. The time for acknowledgements after the transmission of each frame must be reserved on the channel and then the time for re-transmitting the frame (potentially multiple

times) until it is correctly received must also be considered. Therefore, ARQ can often lead to a significant (and also variable) delay.

- F. **Queuing Delay at DLL**: According to a prioritization concept, multiple queues with different priorities may be used at the DLL. Data frames with higher priority may be transmitted before those with lower priority. Therefore, a delay may be incurred as frames wait within the queue before they are selected for transmission.

- G. Channel Access Delay: Wireless technologies, PLC and other wired data busses (e.g. CAN) have one thing in common, namely a shared channel. This means that time division multiple access<sup>5</sup> is often used in order to share the transmission channel<sup>6</sup>. Therefore, each transmitter must wait a certain amount of time until the Medium Access Control (MAC) protocol grants it access to transmit on the channel. This waiting time is the channel access delay.

- H. **Routing Delay**: In multi-hop networks repeater nodes may need to forward packets at each hop. A routing protocol is required in order to dynamically determine routes through the network. Route setup and maintenance is required and during these times packets may need to be queued for later delivery. Also the forwarding process will lead to additional delays as the packets traverse multiple hops. All these delays can be grouped under routing delay.

- I. **Retransmission Delay**: Certain transport layer protocols such as TCP use a retransmission mechanism. This retransmission mechanism will lead to delays similar to that mentioned previously for the ARQ delay.

- J. **Queueing Delay at Transport Layer**: Also at the Transport layer queues are typically used. Datagrams may be segmented and require re-assembly which will also lead to delays.

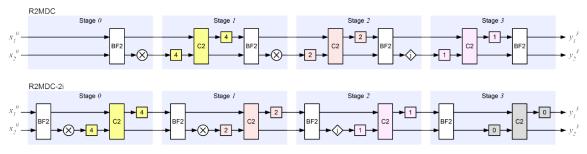

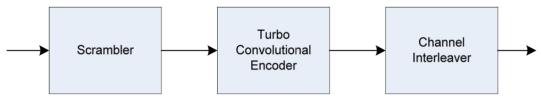

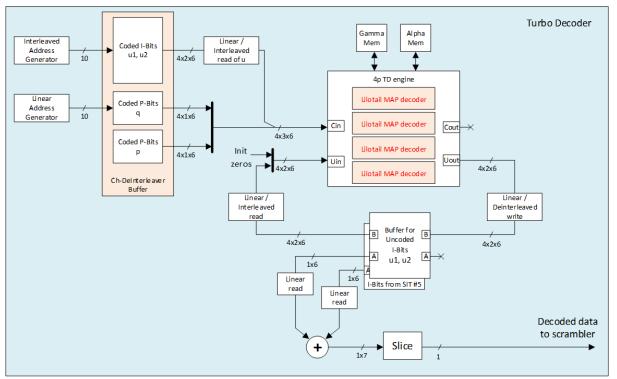

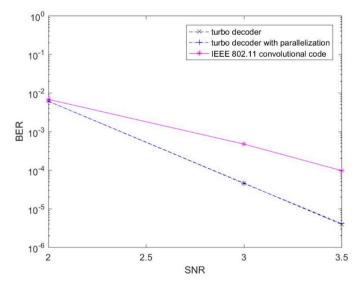

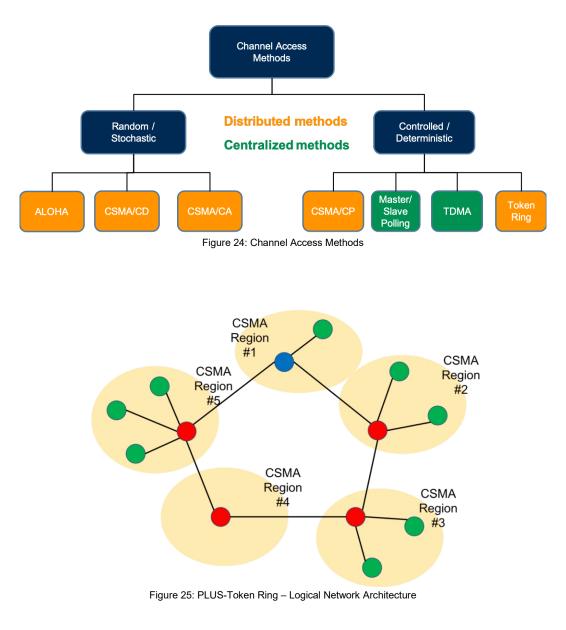

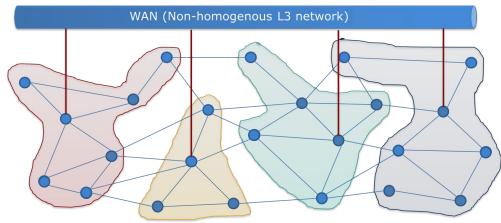

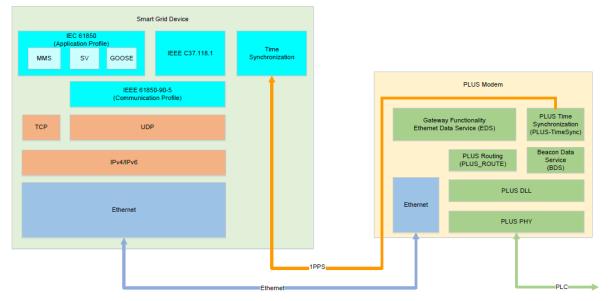

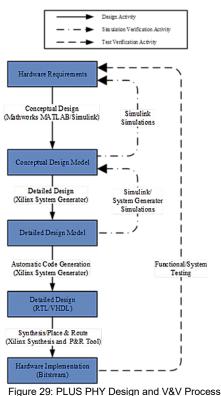

- K. **Connection Setup Delay**: Connection-oriented transport layer protocols such as TCP require a connection between sender and receiver to be established. The connection is established through a handshake mechanism which requires a certain time before which datagrams cannot be delivered.